# Optimizing SiC MOSFET Chip and Packaging Design to Match Specific Application Requirements

David Levett 16<sup>th</sup> Nov 2021

# 2010

**Si IGBT Low Switching Loss**

**UPS**

**Motor Drives**

# 2025?

Si IGBT Automotive

???

**SiC MOSFET Solar**

**SIC MOSFET Energy Storage**

**SIC MOSFET Avionics**

**Si IGBT Servo Drives**

### Program

#### Introduction

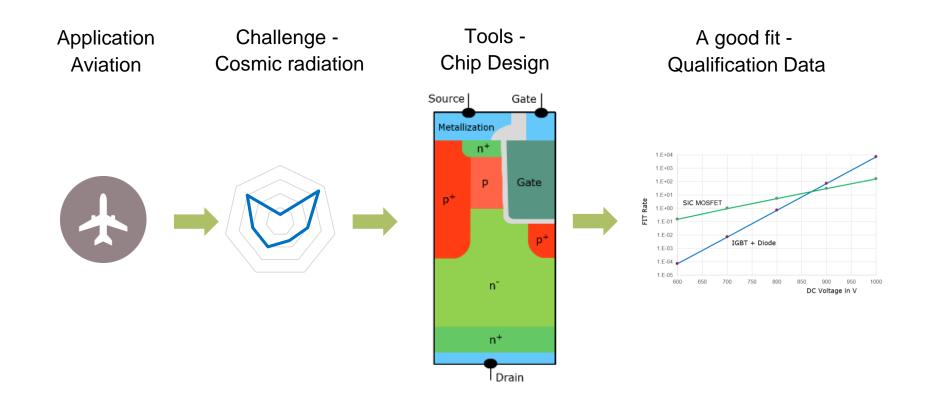

#### **Applications:**

- Aviation Cosmic ray robustness.

- Servo Motor Drives Short circuit capability.

- Traction/CAV Low conduction losses.

- ESS and Chargers Low switching losses.

- Automotive Temperature cycling and EMI.

- What the future holds for SiC MOSFETs?

Q&A

## Overview

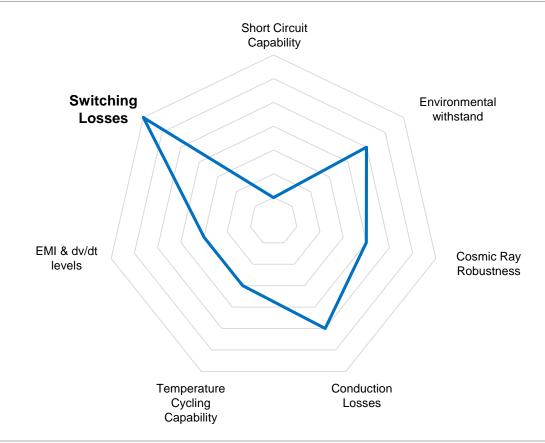

#### **5 Applications**

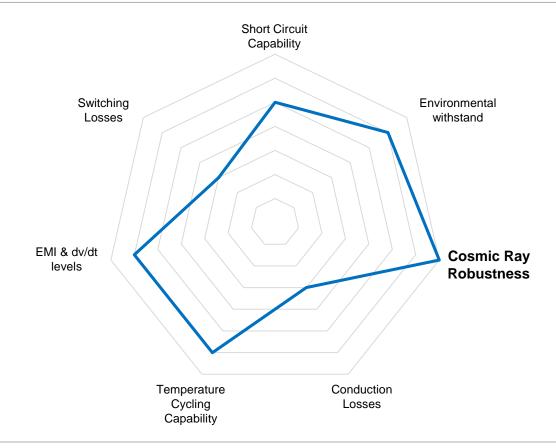

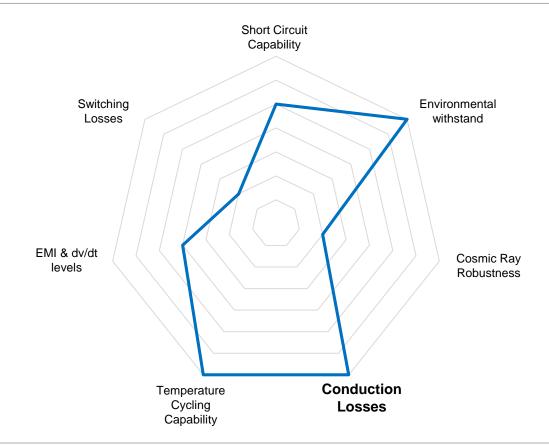

#### 7 Key Parameters

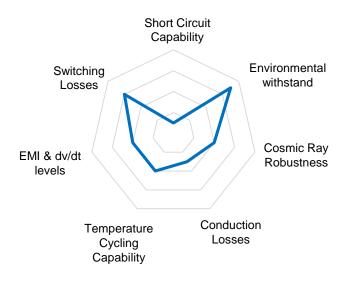

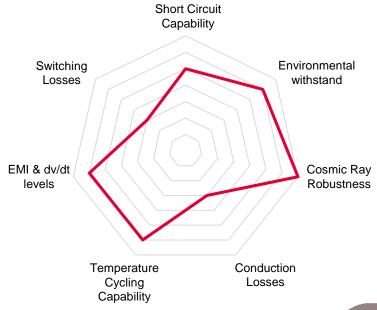

Note Spider diagram "scores" are somewhat subjective

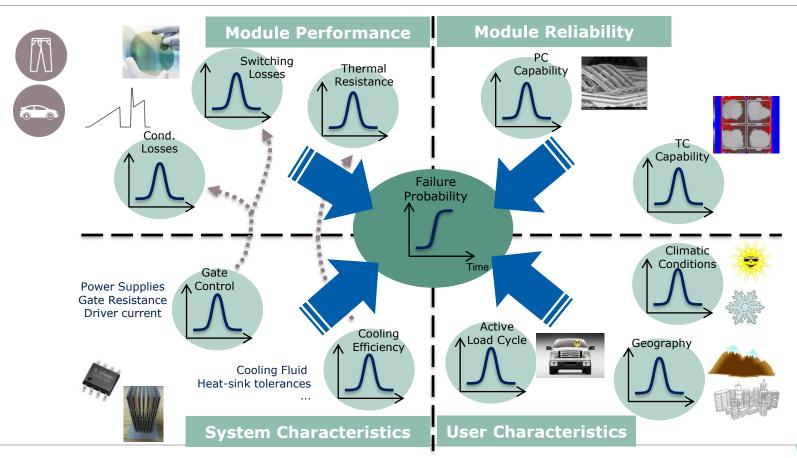

# 3 Aspects for consideration by design engineers

What are the challenges?

Tools to meet challenges

A good fit?

# Seven Design Aspects for a Power Converter

What are the challenges?

# What tools do we have to meet the challenges

#### How to ensure a part is a good fit for the end application?

EconoDUAL™3 Modul mit TRENCHSTOP™ IGBT7 und Emitter Controlled 7 Diode und NTC EconoDUAL™3 module with TRENCHSTOP™IGBT7 and Emitter Controlled 7 diode and NTC

#### Vorläufige Daten / Preliminary Data

#### Potentielle Anwendungen

- Hochleistungsumrichter

- · Hybrid-Nutzfahrzeuge

- Motorantriebe

- Servoumrichter

- USV-Systeme

#### I<sub>C nom</sub> = 900A / I<sub>CRM</sub> = 1800A Potential Applications

- · High power converters

- Commercial Agriculture Vehicles

- · Motor drives

- Servo drives

- UPS systems

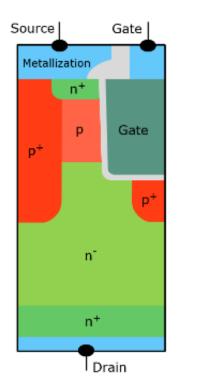

# SiC MOSFET – Basic Properties

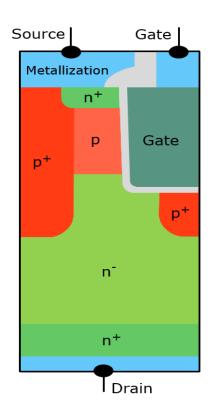

#### Compared to a Si switch

- There is also a MOS (trench) cell on top of a SiC switch

- However the n<sup>-</sup> drift zone can be built much thinner and doped at a higher level resulting in lower Ron and lower switching losses

| physical properties             | 4H-SiC  | Si       |  |

|---------------------------------|---------|----------|--|

| band gap [eV]                   | 3.26    | 1.12     |  |

| break through field [MV/cm]     | ~2.5    | 0.25     |  |

| thermal conductivity [W/cm/K]   | ~3.4    | 1.5      |  |

| ideal bulk mobility [cm²/V/s]   | 800/115 | 1400/450 |  |

| electron saturation vel. [cm/s] | 2e7     | 1e7      |  |

Driftzone Thickness: SiC/Si: ≈ 1/10

Driftzone Doping: SiC/Si: ≈ 100/1

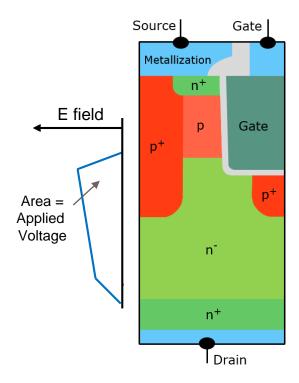

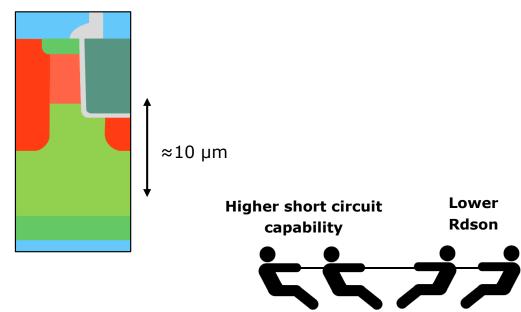

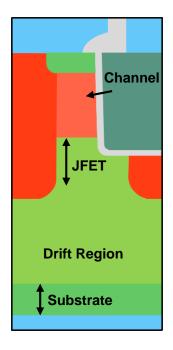

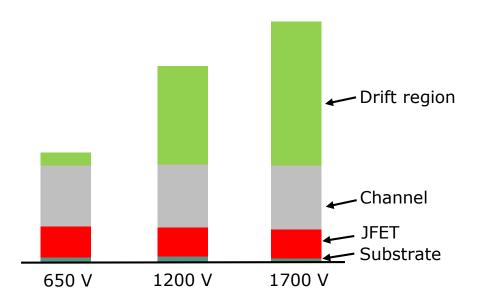

# IGBT Transistor Cell Cross Section Typical sizes for a 1200 V device IGBT and SiC MOSFET

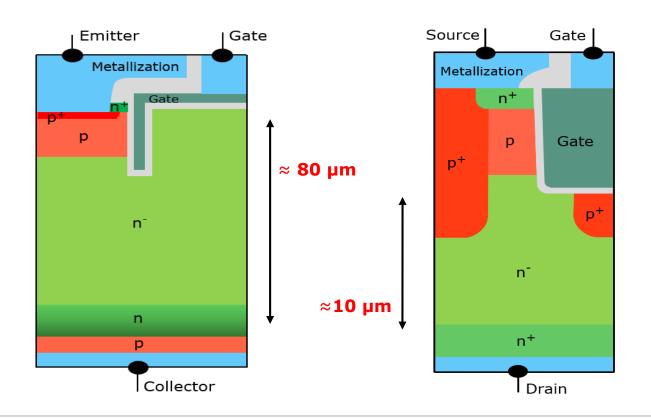

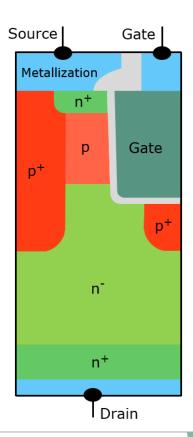

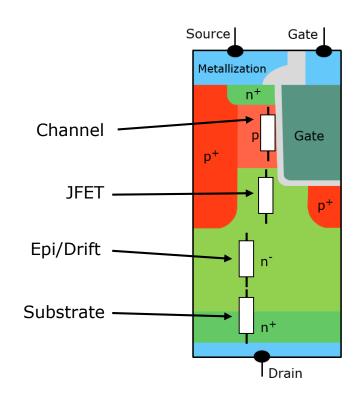

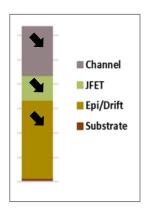

# SiC MOSFET – Key Elements

#### **Trench Cell with**

- MOS channel in a specific crystal orientation for a good channel mobility.

- Shielding of the gate oxide against high electric field strength in the on and off condition by special p<sup>+</sup> doping (to make the gate oxide stress comparable to Si devices).

- p<sup>+</sup> doped layer also serves as a good body diode ("p-emitter").

#### **<u>Drift Zone</u>** with adequate

- Thickness

- Doping

To ensure required blocking voltage combined with low on state resistance.

# SiC MOSFET – Four Main Components of R<sub>DSON</sub>

# Overview an Example

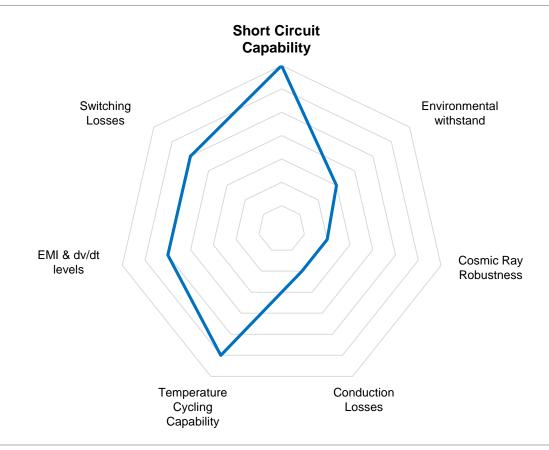

# Aviation- Spider Diagram

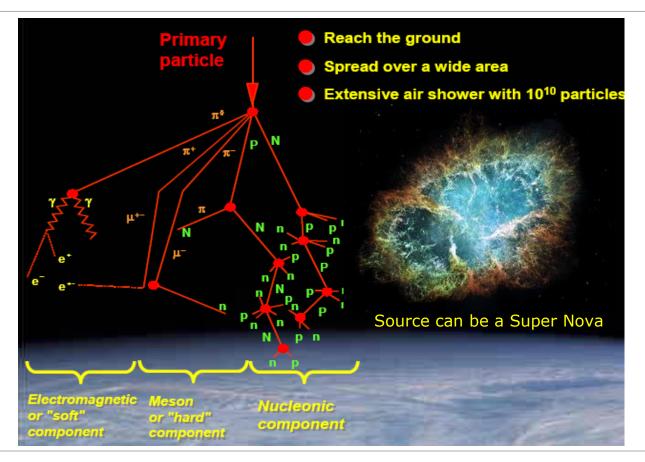

# What is **C**osmic **R**adiation CR?

#### Cosmic Radiation CR

## **Cosmic Radiation**

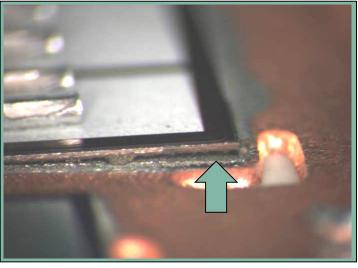

Top side view of a failure

1 FIT (Failures In Time) = one failure in 10<sup>9</sup> operation hours of the device.

Note only in reverse blocking condition

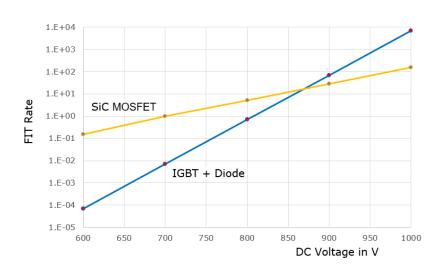

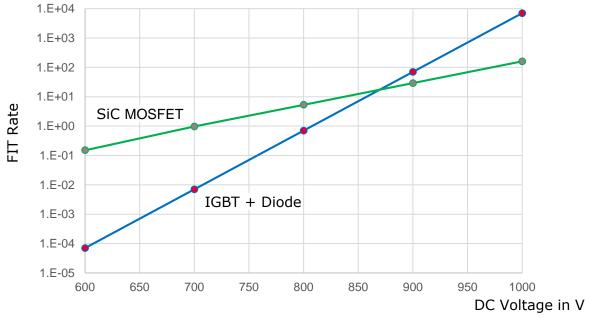

# Typical CR FIT Values for a 1200 V 200 A Si and SiC Based Half Bridge at 25 °C and Sea Level

Some differences between SiC MOSFET and Si IGBT + Diode:

The SiC MOSFET has a smaller active area than the Si IGBT/Diode for the same current, does not need a free

wheeling diode, has a much thinner drift zone, but higher electrical field strength.

In this specific example for 1200V class devices the SiC MOSFET has a flatter gradient than the equivalent Si device, however in most cases (depending on the choice of devices and voltage classes) the slopes are quite similar.

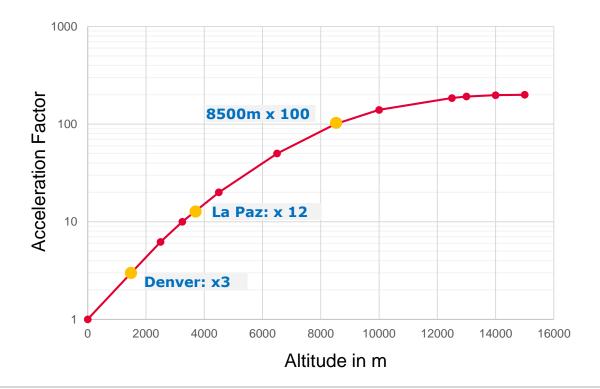

# So Why Aviation?

## So What is the Failure Rate? An Example.

## A single module has a failure rate of 10 FIT at sea level

- ⇒ Each converter has 6 modules = 60 FIT

- ➡ Each aircraft has 8 converters = 480 FIT

- → Aircraft at 8500m altitude = 48,000 FIT

- → A fleet of 100 aircraft = 4,800,000 FIT

So if each plane operates at altitude 6 hours a day there could, statistically, be a failure every month.

# Chip Design Tools

Key is to reduce the field strength in drift region. This can be done by doping in the drift region to flatten out the electric field. The area is still the same the but peak lower.

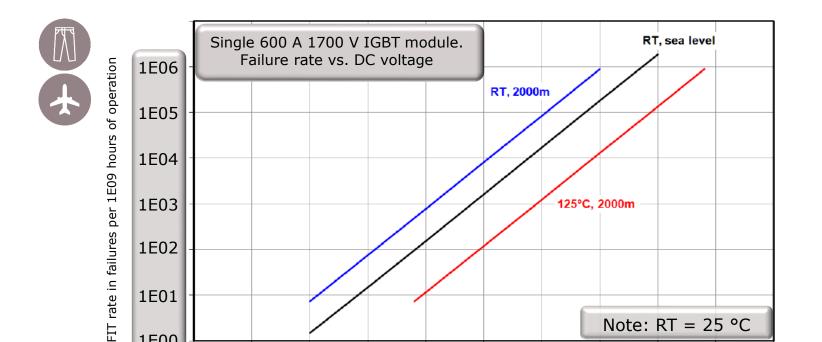

# Cosmic Radiation Failure Rates – Typical Values

1E00

1000

FIT rate for this Si IGBT reduces with: lower voltage, lower altitude and higher temperature.

DC Applied Voltage in Volts

1300

Note: RT = 25 °C

1500

1400

1200

1100

# Failure Rate Estimation Using a Mission Profile

| Time each Day in minutes | Altitude<br>in m | Applied<br>Voltage in V | Temperature<br>in °C | FIT rate per day<br>per module |

|--------------------------|------------------|-------------------------|----------------------|--------------------------------|

| 30                       | 5000             | 800                     | 75                   | 0.002                          |

|                          |                  |                         |                      |                                |

## Summary

- Cosmic radiation can cause random power semiconductor failures.

- Voltage and altitude are key factors.

- Partnering with supplier and running a mission profile calculation can provide estimation of field failure rates.

# Servo Drives - Spider Diagram

# Why Do Servo Motors Need Short Circuit Protection?

# Why Do Servo Motors Need Short Circuit Protection?

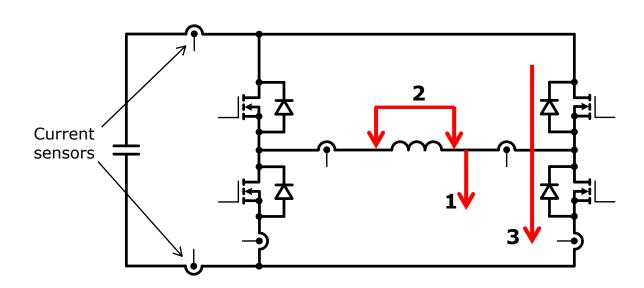

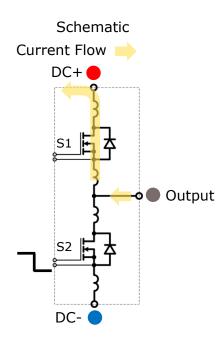

#### Short Circuit – Three Main Paths

Three main short circuit Paths:

- 1. Phase to ground

- 2. Phase to phase

- 3. Shoot through

Three main locations for current sensors:

- > DC Bus

- Power Source

- Output Phase

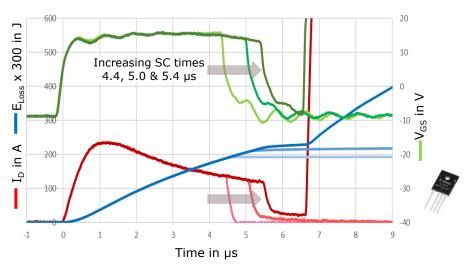

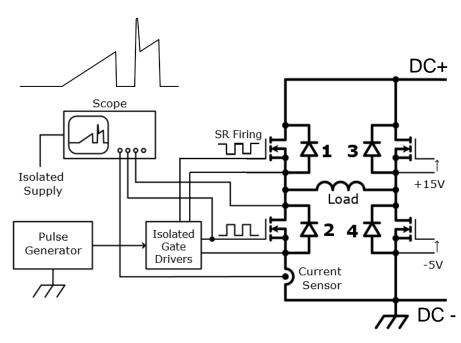

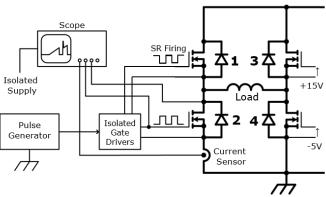

# SiC MOSFET Short Circuit Testing

Operating point:  $V_{GS} = -9 \text{ V} / +15 \text{ V}$ . VDC=800 V, Isc=240 A@ 25 °C

Failure at 5.4 µs

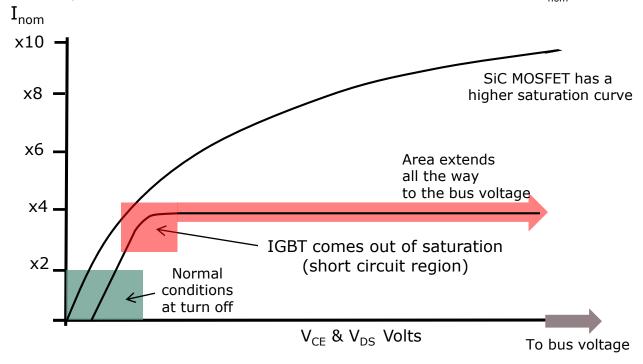

# Why More of an Issue for SiC MOSFETS? Typical IGBT and SiC MOSFET De-Saturation

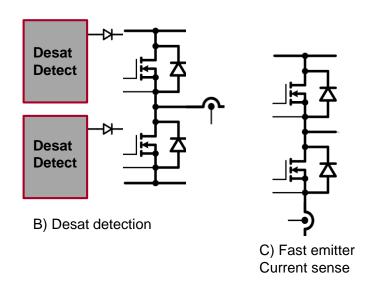

Short circuit conditions can be detected by measuring the  $V_{CE}$  or  $V_{DS}$  value when the IGBT/MOSFET is turned on. The IGBT comes out of saturation at lower  $I_{nom}$  current levels.

# Why More of an Issue for SiC MOSFETS?

#### **Smaller chip size**

100 A SiC MOSFET Total Area ≈ 30 mm<sup>2</sup>

100 A IGBT

Total Area  $\approx 115 \text{ mm}^2$

#### **Losses in thin layer**

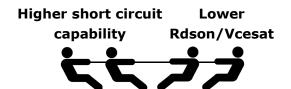

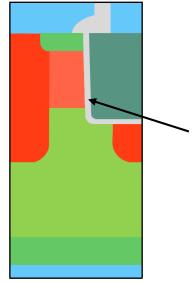

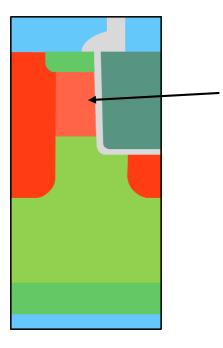

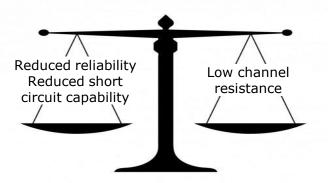

# Chip Design Tools to Influence Short Circuit Robustness

The longer channel and narrower the channel width the lower the short circuit current but higher the Rdson

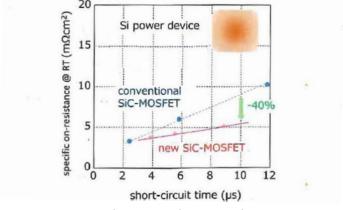

# Chip Design Measures to Influence the Short Circuit Robustness

Curves showing Rdson vs. short circuit time for SiC MOSFET chip design. (8)

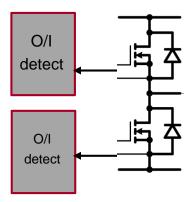

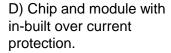

# **Short Circuit Protection Some Options**

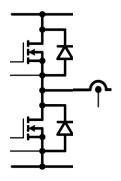

A) No desat detection

Fast current sensors

No shoot through protection

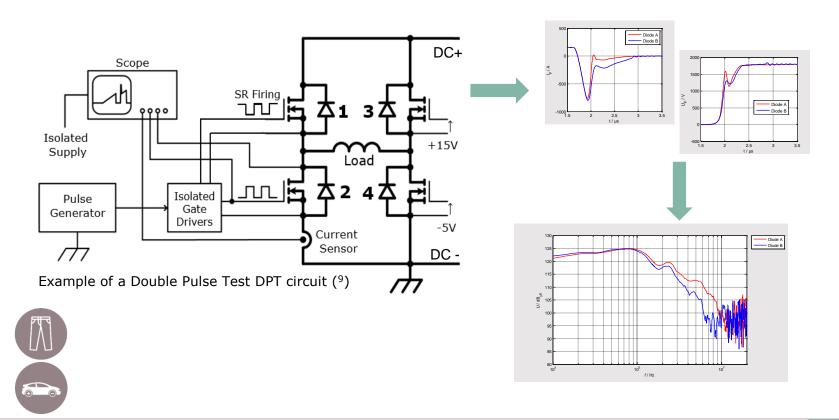

## **Short Circuit Capability Testing**

Example of a Double Pulse Test DPT circuit (9)

### Summary

- Protection under short circuit conditions always has a cost either in terms of system layout, gate driver design or chip performance.

- If required check data sheet carefully and perform

Double Pulse Test DPT of the device in situ.

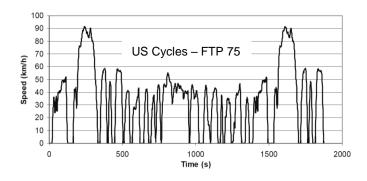

## Requirements of Traction and Commercial, Construction and Agricultural Vehicle CAV Drives

- Long Operating life >20 years and > 60,000 hours.

- High mechanical vibration and shock.

- High cyclical loads and high torque at zero speed/locked rotor.

- Low switching frequency and conduction losses dominate.

## Traction Drives- Spider Diagram

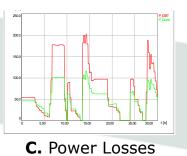

## Why Conduction Losses are Dominant for High Power Traction Drives

A 1000A 1700V IGBT Operating at 800 rms 500Hz Fsw. Switching losses = 12% Conduction losses = 88%

A 3 m $\Omega$  1200V SiC MOSFET Operating at 300 rms 2000Hz Fsw. Switching losses = 20% Conduction losses = 80%

## Components of R<sub>DSON</sub> of a SiC MOSFET

Unlike IGBT  $R_{DSON}$  is  $\approx$  linear with current

## Tools for R<sub>DSON</sub> Reduction - Channel

Trench gate at 4° for lowest level of crystal defects.

Channel: Higher gate voltage/thinner gate oxide layer = lower gate oxide reliability & lower short circuit capability

### Paralleling Devices to Reduce Conduction Losses

Conduction Losses IGBT 1 module 2 modules

≈ 30% reduction

Conduction Losses SiC MOSFET

1 module

2 modules

≈ 60% reduction

Note loss reduction >50% due to reduced  $T_{\rm j}$

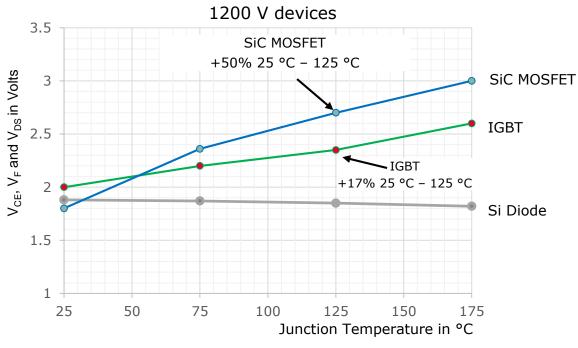

## V<sub>CE</sub>, V<sub>F</sub> and V<sub>DS</sub> Dependency on Temperature

SiC - much larger dependency of conduction losses with temperature than IGBT and Si Diode

## Variation of $R_{DSON} / V_{CE}$ with $V_{GS} / V_{GE}$

SiC - much larger dependency of conduction losses with gate voltage than IGBT and Si Diode

## Energy Storage and Chargers – Spider Diagram

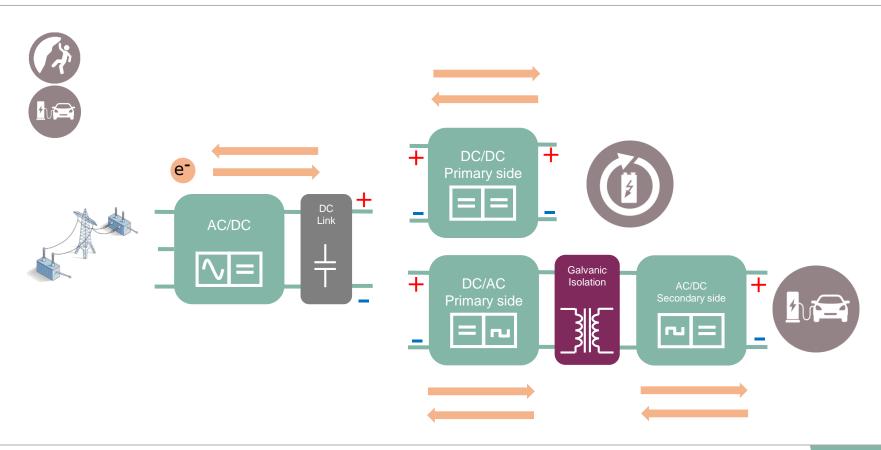

## A Day at the Office for an Electron

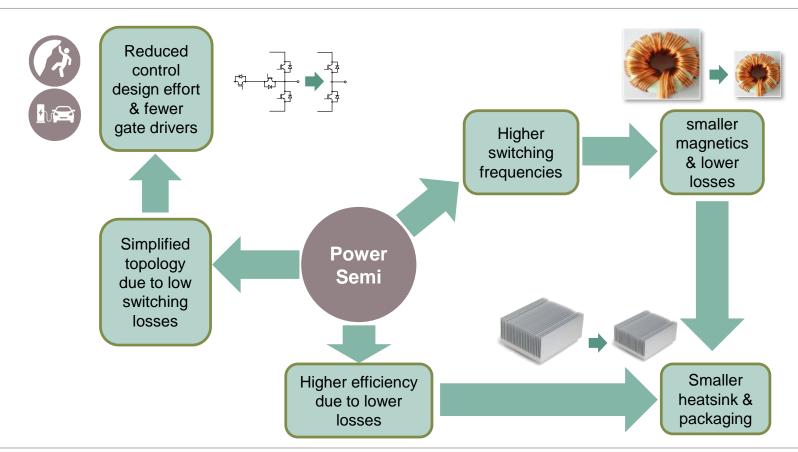

## Benefits of Higher Switching Frequencies

## Chip Design Measures for low switching losses

Relax SiC MOSFETs have low switching losses

## Challenges of Fast Switching

EMI – dv/dt and di/dt

### Voltage Over-shoots and RBSOA

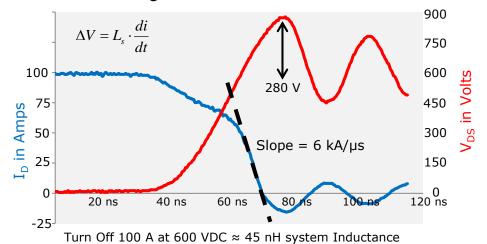

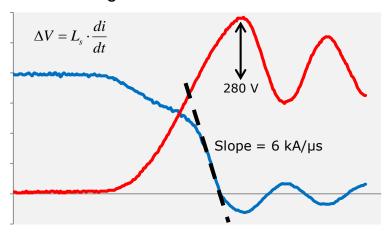

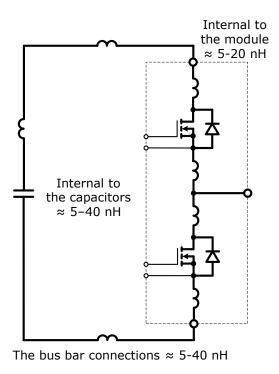

## How to Reduce Voltage Overshoots and Oscillations at Turn Off

- Reduce the di/dt level

- Reduce the loop inductance

### Voltage Over-shoots and SOA

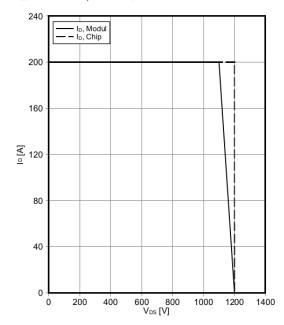

## Typical SOA curve for a 100A 1200V SiC MOSFET module

#### safe operating area MOSFET (SOA)

$I_D = f(V_{DS})$  $V_{GS} = -5V/+15V$ ,  $T_{vi} = 150$ °C,  $R_G = 3.9\Omega$

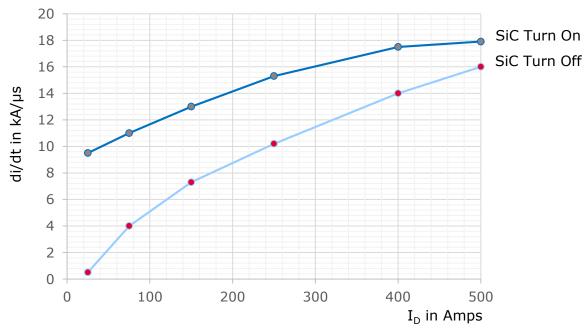

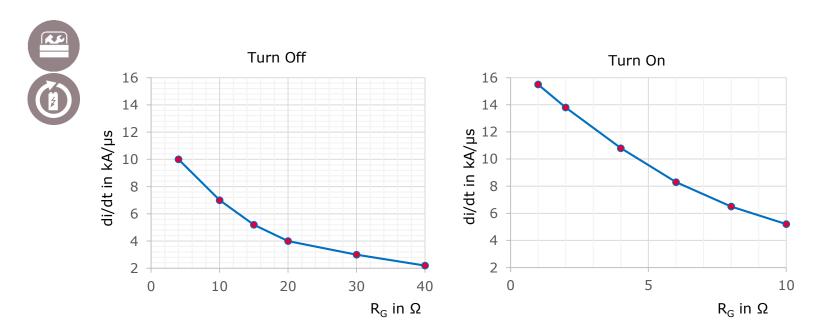

## Typical di/dt levels for 200 A SiC MOSFET switching at 150 °C

Turn off at 250A with  $L_s \approx 30$  nH and 10.2 kA/ $\mu$ s  $\approx 306V$  overshoot

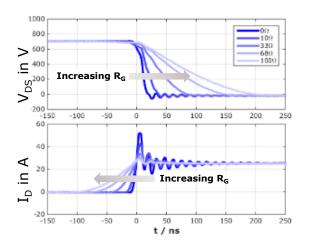

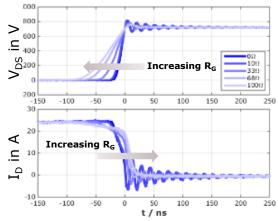

## SiC MOSFET Controllability of Switching Speed Using R<sub>G</sub>

# Typical di/dt levels for 200 A SiC MOSFET switching at 150 °C, 250 A with Changing R<sub>G</sub>

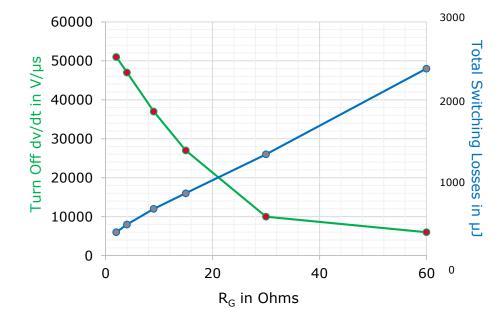

By increasing R<sub>G</sub> from 3.9  $\Omega$  to 20  $\Omega$  the voltage overshoot is reduced from  $\approx$  306 V to 30 nH x 4 kA/ $\mu$ S  $\approx$  120 V overshoot

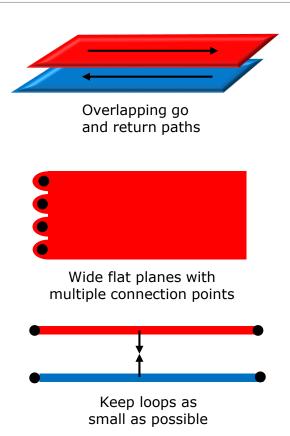

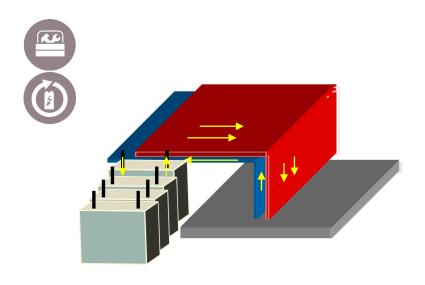

## Where is the System Inductance and How to Reduce it?

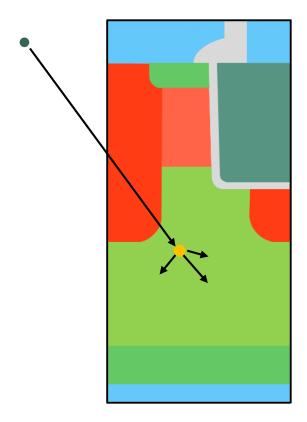

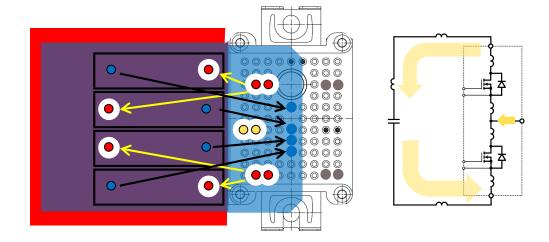

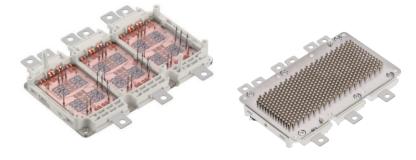

### Low Inductance Module Design

Parallel overlapping planes with multiple connections and small loops

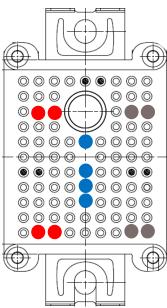

Package Top View

## Current Flow in Both PCB DC Bus Layers

- Short current paths, small current loops, multiple paths in parallel

- If possible, current flowing in opposite planes

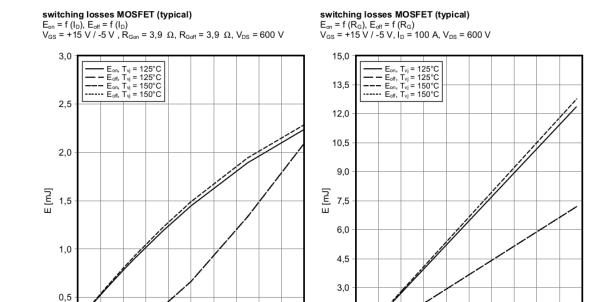

## Data Sheet Switching Performance Curves

Typical Curves for 100A 1200V SiC MOSFET Module

1,5

12 16 20 24 28 32 36 40  $R_G[\Omega]$

80 100 120 140 160 180 200 I<sub>D</sub>[A]

### How to Confirm Switching Loss Performance

- Switching losses in the final application will be different from data sheet due to different operating conditions and gate driver.

- Strongly recommended to run Double Pulse

Test DPT in final application system.

- Review di/dt and dv/dt levels and leave margin for higher Rg values if required.

### Summary

- With magnetics increasing switching frequency can reduce size, cost and weight.

- Chip design compromises especially with increased on state losses are required.

- Increasing gate resistor values can reduce EMI and di/dt levels but at a cost of higher switching losses

- Application factors such as low inductance layout and low EMI design need to be considered.

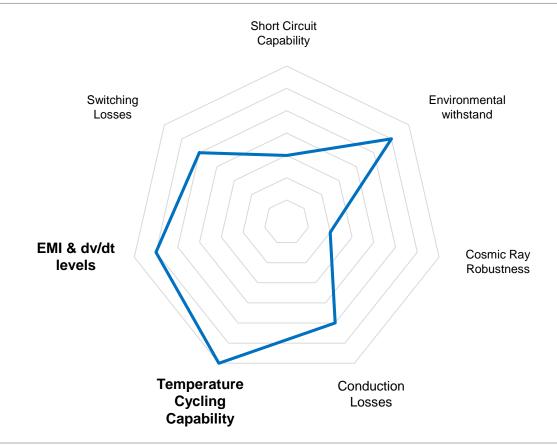

## Automotive –Spider Diagram

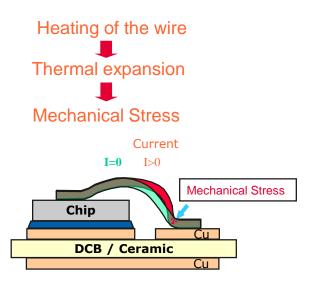

## Challenge Cyclical Load – High Temperature Cycling

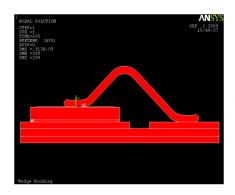

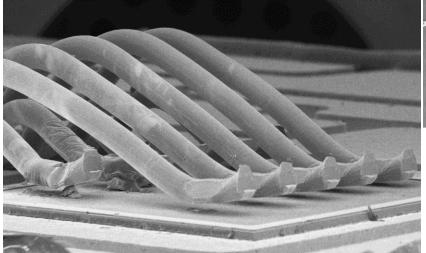

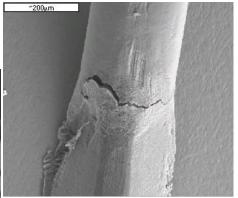

# What are the Wear Out Mechanisms due to Temperature Cycling? Bond Wire Fatigue.

Bond wire fatigue caused by

- a) Thermally induced movement of the bond wire

- b) Fatigue of welding area due to by thermal mismatch Al vs. Si

Bond Wire Lift Off

Bond Wire Heel Crack

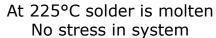

## Chip Solder and SiC Chip Stress Caused by Temperature Cycling

|        | СТЕ                                      | Young's<br>Modulus |

|--------|------------------------------------------|--------------------|

| Si     | $\approx 2.6 \times 10^{-6} / ^{\circ}C$ | ≈ 62 GPa           |

| SiC    | ≈ 4 x 10 <sup>-6</sup> / °C              | ≈ 450 GPa          |

| Solder | ≈ 23 x 10 <sup>-6</sup> / °C             | ≈ 40 GPa           |

| Copper | ≈ 17 x 10 <sup>-6</sup> / °C             | ≈ 117 GPa          |

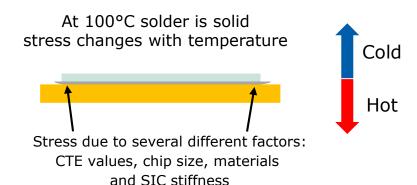

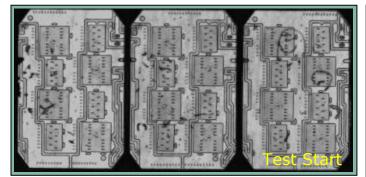

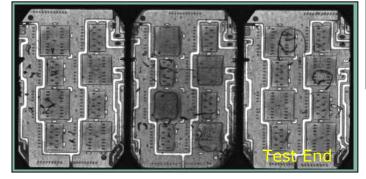

## Chip Solder Delamination

Ultra Sonic scans of the chip soldering layer

Optical image of delaminated chip solder

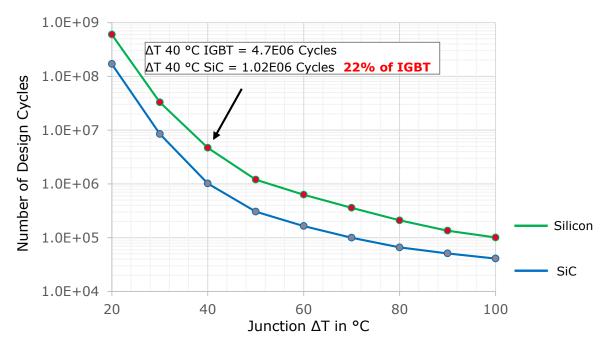

# Typical Power Cycling Capability Curves SiC & Si IGBT at a Maximum Junction Temperature of 100 °C

Note: Design cycles = Cycles at which 5% of samples show a 5% increase in forward voltage drop

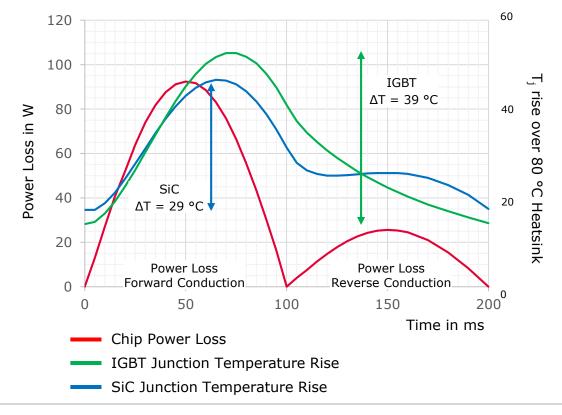

## Ripple Temperature at 5 Hz Operation IGBT & SiC MOSFET

#### Tools to Increase Lifetime

**Emitter**

.XT front metal

.XT back meta

Collector

- Gate > Reduce Losses

- Improve Cooling

- Improve top side joining technology for Example top side copper and bond wires

Improve solder connection e.g. diffusion soldering or sintering

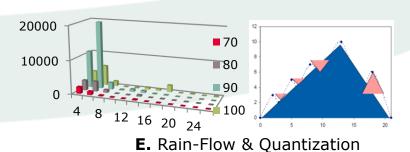

### How is Lifetime Estimated? 7 Steps A-F

**D.** T<sub>1</sub> Thermal Model

1.E+09 1.E+08 1.E+07 1.E+06 1.E+05 1.E+04 20 70 **F.** Design Life

#### Statistical Parameters & Life Time Evaluation

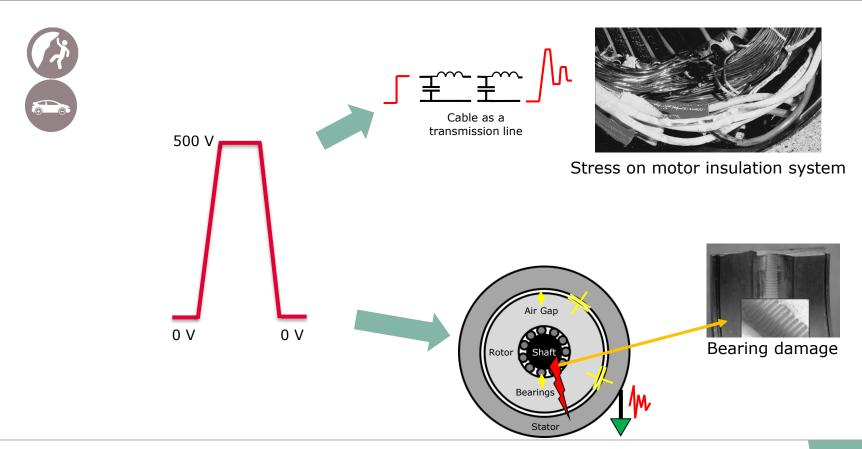

## Challenges: EMI / dv/dt

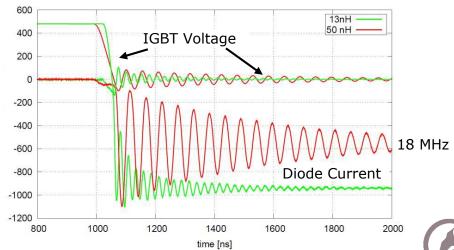

## High di/dt and Loop Inductance = Oscillations

# Lower inductance = reduced oscillations and EMI

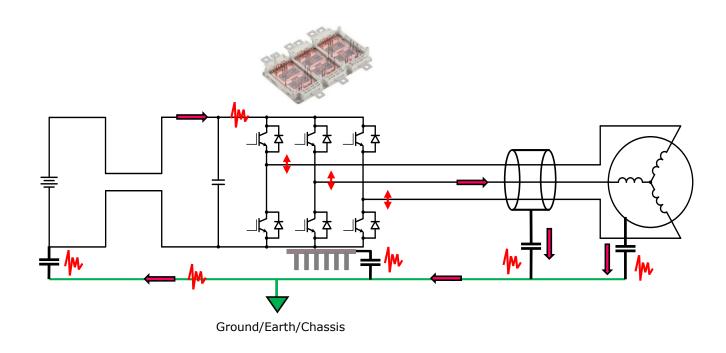

## Typical Paths for Parasitic Current Flow and Conducted EMI

$I = C \times dv/dt$

### Fast Switching Edges at High dv/dt are Problematic

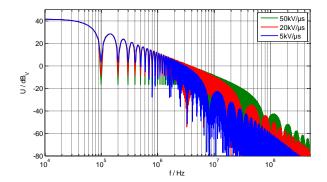

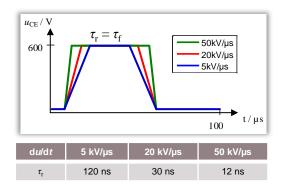

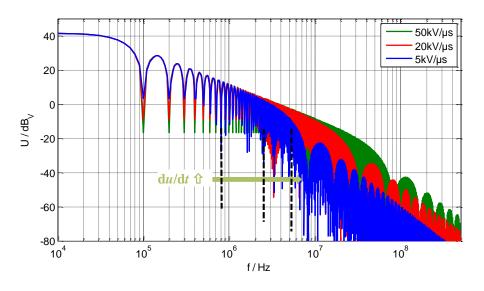

# Ideal Fast Fourier Transformation (FFT) of Trapezoidal Waveform with varying dv/dt slopes.

dv/dt has more effect at the higher frequency region of the spectrum. Here @10MHz: the difference between  $dv/dt = 5 \& 20 \text{ kV/}\mu\text{s}$  is 15 dB(V)

# Typical dv/dt levels and Switching Losses vs. R<sub>G</sub> for a SiC MOSFET

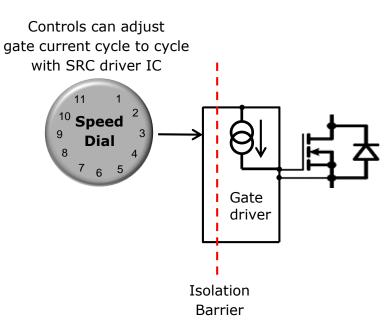

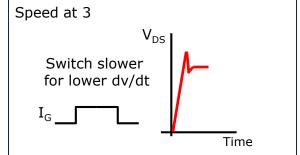

# Slew Rate Control SRC: Adjustable Switching Speed Cycle to Cycle Using Current Source.

# Double Pulse Test Waveforms can be Used to Simulate Plots

### Summary

- A very complex design challenge, difficult to simulate and measure.

- Keep power switching loops small and minimize inductance.

- Understand capacitance paths to ground and steer/route parasitic currents to selected paths.

- Check switching waveforms using DPT over the full range of currents, voltages and temperatures.

- Switching speeds can be reduced by Rg and Cge/Cgs or new gate driver technology but all will increase switching losses.

### The SiC MOSFET Situation Today

Different SiC MOSFET concepts exist:

#### Cell:

Planar cell MOSFETs and Trench cell MOSFETs.

# Different Freewheeling **Diode** concepts:

Freewheeling diode function externally as a SiC schottky diode or as integrated SiC schottky or as p-body diode.

#### **Vertical** concept:

So far conventional uniform drift zone doping.

# What else to Come? Strong R<sub>DSON</sub>\* Area Reduction Forseeable

- Cell concept:

- Trend to trench.

- Most likely advanced trench concepts will follow later step by step (similar to low voltage Si Power MOSFETs).

- Vertical concept:

- SuperJunction very attractive from performance perspective, but pro's and con's need to be assessed.

- Higher junction temperatures (similar as for Si IGBTs, but even more...), also in this case pro's and con's need to be assessed. Note strong R<sub>DSON</sub> increase with temperature.

- Advanced assembly and interconnect technologies (at least as important as for Si IGBTs).

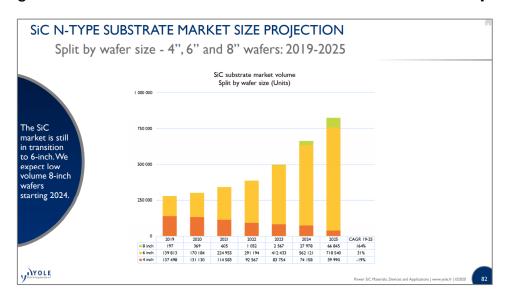

# What else to Come? Strong SiC Production Capacity Increase Foreseeable

Larger SiC Wafer Diameter 150 mm => 200 mm: more chips out of one wafer

To overcome the SiC Material Irony -

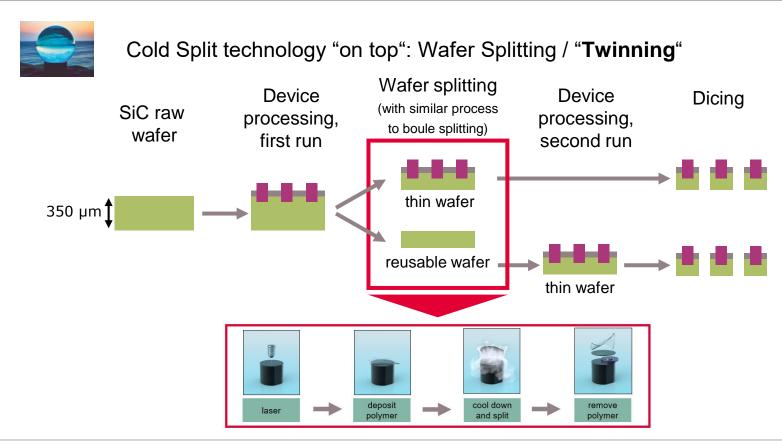

... Boule and wafer **splitting** to **make more SiC wafers out of a single SiC boule**

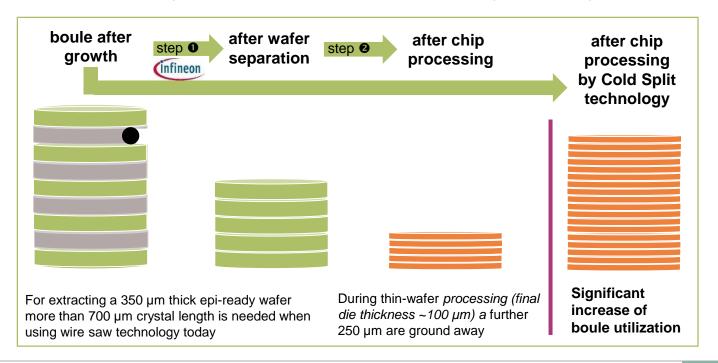

# Strong SiC Production Capacity Increase Foreseeable - the SiC material irony

- The SiC boule growth process is expensive and time-consuming

- Today, ¾ of the grown material is turned into dust during processing

## Strong SiC Production Capacity Increase Foreseeable

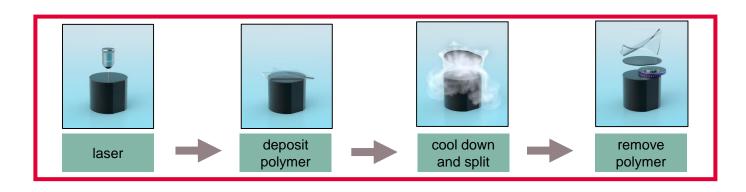

- Cold Split Technology

#### Cold Split technology at a first glance: Boule Splitting

## Strong SiC Production Capacity Increase Foreseeable

- Cold Split Technology

### Summary

- Cell concept: Trend to trench, most likely advanced trench concepts will follow a step at a time.

- Vertical concept: SuperJunction very attractive from performance perspective, however pro's and con's to be assessed.

- Higher junction temperatures may come, if advantageous.

- Advanced assembly and interconnect technologies (at least as important as for Si IGBTs).

- Larger SiC Wafer Diameter 150mm => 200mm: more chips out of one wafer.

- Boule and Wafer Splitting to make more SiC wafers out of a single SiC boule.

- A bright future ahead ... for SiC / WBG for sure, but also Si IGBTs with cost and performance improvements they will remain very important.

#### References

- How Infineon controls and assures the reliability of SiC based power semiconductors. A White Paper.

- Failure rates of HiPAK modules due to cosmic radiation. Application note 5SYA2042-04. ABB.

- 3.

- What stresses power semiconductors in Photovoltaic applications. Dr. Regine Mallwitz SMA. Requirements for future simulation tools from an industrial point of view. F.Pfrsch EPCE 2012 Infineon Technologies. 4.

- T.Laska et. al., "Short Circuit Properties of Trench-/Field-Stop-IGBTS Design Aspects for a superior Robustness", Proc. of ISPSD, 2003

- M.Otsuki et. al., "Trends and Opportunities in Intelligent Power Modules (IPM)", Proc. of ISPSD, pp. 317-320, 2015

- F.Hille et. al., "Reliability aspects of copper metallization and interconnect technology for power devices", Proc. of ESREF, 2016

- Bodo's Power Systems Sept 2018 P26.

- D.Levett et.al., "Double pulse testing the how, what and why. Bodo's power systems April 2020"

- Ingo Voss et.al., "Reliability and Ruggedness of SiC Trench MOSFETs for Long-Term Applications in Humid Environment", PCIM 2018.

- 11. Kaminski, N. "Reliability Challenges for SiC Power Devices in Systems and the Impact on Reliability Testing". Materials Science Forum, 924, 2018, S. 805-810.

- 12. C. Zorn et.al., "Temperature Humidity Bias (THB) Testing on IGBT Modules at High Bias Levels", CIPS 2014; 8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 2014, 2014, S. pp. 1-7.

- 13. Reference Book. IGBT Modules Technologies, driver and application. 2<sup>nd</sup> edition paperback. 3<sup>rd</sup> edition hardback.

- 14. Wolfspeed/Cree. Application Considerations for Silicon Carbide MOSFETs.

- 15. Infineon AN2017-14. Evaluation Board EVAL-1EDI20H12AH-SIC.

- 16. Agile Switch APEC 2017. Driving Silicon Carbide Power Modules Efficiency & Reliability 17. Infineon AN2017-46. CoolSiC™ 1200 V SiC MOSFET Application Note

- 18. Power Integrations/Concept, AN9701 IGBT drivers correctly calculated.

- 19. J.Howes et.al., "Temperature limits for power modules Parts 1 & 2". Bodo's Power Jan & March 2016.

- 20. Boule splitting: https://www.infineon.com/cms/en/about-infineon/company/siltectra/

- 21. H.Fels et.al., "The CIBH diode great improvements for ruggedness and softness of high voltage diodes, Proc. Of ISPSD, pp173-176, 2208

SiC MOSFET application notes on Infineon website at: https://www.infineon.com/cms/en/product/power/wide-band-gap-semiconductors-sic-gan/siliconcarbide-sic/coolsic-mosfet/#!documents Then page down for application notes Application notes and data can also be obtained from your local sales representative.

Part of your life. Part of tomorrow.