# **Final Report**

September 2021

**DOE Cooperative Agreement DE-EE0006521**

North Carolina State University

**Executive Director and CTO: Victor Veliadis**

# **Table of Contents**

| Executive Summary                   |     |

|-------------------------------------|-----|

| 2015 Highlights                     |     |

| Operations and Management           |     |

| Education and Workforce Development | 20  |

| Mambar Accomplishments              |     |

| Member Accomplishments ABB          | 29  |

| Arizona State University            | 2)  |

| Dr. Choudhury                       | 35  |

| Dr. Raja Ayyanar                    |     |

| Cree Fayetteville                   |     |

| Cree/Wolfspeed.                     |     |

| Delphi                              |     |

| Florida State University            |     |

| GeneSiC                             |     |

| John Deere                          |     |

| Monolith                            |     |

| North Carolina State University     |     |

| Dr. Jay Baliga                      | 107 |

| Dr. Subhashish Bhattacharya         |     |

| Dr. Iqbal Husain                    |     |

| Dr. Srdjan Lukic                    |     |

| Dr. Veena Misra                     |     |

| Dr. Mehmet C Ozturk                 |     |

| National Renewable Energy Lab       |     |

| Naval Research Laboratory           |     |

| Toshiba                             |     |

| Transphorm                          | 172 |

| UC Santa Barbara                    |     |

| USCi                                | 183 |

| Virginia Tech                       | 193 |

| X-Fab                               | 204 |

# **Executive Summary**

PowerAmerica: The Next Generation Power Electronics Manufacturing Innovation Institute has been established and is making significant progress in furthering the program goals of accelerating the adoption wide bandgap semiconductors into power electronics technologies, to spark early commercialization of compact, robust, energy efficient products, and to nurture the U.S. wide bandgap semiconductor industry by developing a capable workforce though education programs and training. The PowerAmerica consortium, led by NC State University, is accomplishing this through a cooperative agreement with the U.S. Department of Energy (DOE) Office of Energy Efficiency and Renewable Energy's Advanced Manufacturing Office. This private public partnership with EERE includes member companies ranging from startups, smallmedium enterprises, to large system integrators, world class universities and community colleges, K-12 educational institutions, trade associations, state and federal government agencies, and economic development organizations. The wide bandgap power electronic ecosystem formed by this diverse set of Institute members is focused on using advanced manufacturing to 1) lower the cost of silicon carbide and gallium nitride devices to be comparable to silicon devices, 2) demonstrate the size, weight and energy efficiency advantages of wide bandgap semiconductor power electronics through world class demonstrations of capability that translate into new products for US industry that create jobs and 3) building an education pipeline for a skilled workforce to meet the future demand for emerging wide bandgap semiconductor power electronic markets to enhance US economic competitiveness globally.

The first year has laid the groundwork for a successful sustainable program that is driven by industry's needs. Infrastructure has been established to ensure industry proprietary information is securely protected, while channels for dialog and communication across the supply chain are enhanced. Formulation of an open source process model for wide bandgap semiconductors, (similar to open source software licensing) is being investigated as a mechanism for industry to mutually invest in wide bandgap semiconductors while maintaining the appropriate control of proprietary information. Strong relationships between university faculty and industry members is leading to technology partnerships that enhance movement up the Technology and Manufacturing Readiness Level scales, that will lead to new product introduction and technology transition.

Under the leadership of Executive Director Nickolas Justice and Deputy Director Dr. John Muth, the PowerAmerica staff and the industry and university partners continue to focus on US competitiveness, guided by the industry voice to shape a wide bandgap power electronic roadmap for the future. In addition to the open source fabrication of wide bandgap semiconductor devices and projects targeted at specific technology achievements, the sustainability initiatives include a new teaching-manufacturing laboratory that cross-cuts Electrical, Mechanical and Industrial Engineering disciplines and has engagement with the College of Management and the School of Design. This new facility represents a significant NC State commitment to the sustainability of the

Institute. The focus on design for manufacture (DFM), design for reliability (DFR) and power electronics assembly will provide a unique capability to engage small-medium enterprises and entrepreneurs in the low and medium volume manufacture of advanced power electronic systems. This serves as a platform to disseminate best design practices and reduce the dependence on contract manufacturing overseas. Similarly, a device "bank" concept is being investigated that will improve the availability and reduce the cost and lead-time of high performance wide bandgap devices. This will allow universities and companies to more easily innovate and build prototypes for demonstration and new product introduction, reducing the time to market and accelerating commercialization.

PowerAmerica is devoted to accelerating the adoption of smaller, lighter, more efficient systems enabled by wide bandgap semiconductors leading to low cost, clean, renewable energy systems, longer-range more efficient transportation, industry and consumer energy savings, smarter electric grids and a better quality of life. As we move into Budget Period 2 and beyond, we look forward to continuing our work with existing members and expanding opportunities with new members to improve US competitiveness in wide bandgap power electronics and building a well-trained, skilled workforce to capitalize on this opportunity.

PowerAmerica Budget Period 1 (2015-2016) Highlights

Focus Area 1: Operations and Management: In the first year, 22 projects were initiated that extend across the supply chain, building US capability in: the fabrication of wide bandgap powers devices; packaging those devices to maximize their electrical and thermal performance; and incorporating those devices into advanced system demonstrations that have strong commercialization potential. Over the course of the year, four high potential, Open Innovation Fund projects complementing the initial projects were also selected, increasing the diversity and capability of the Institute. In response to the Institute's call for proposals, 93 concept papers were received which resulted in 52 full proposal submissions for budget period two. It is anticipated that after rigorous peer reviews, approximately 30-35 new projects will be awarded that will further advance the Institute's goals.

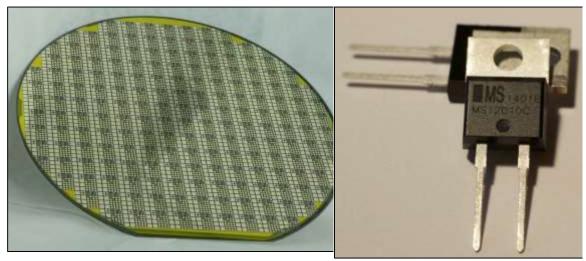

**Focus Area 2: Foundry and Device Development:** The nation's first six-inch diameter silicon carbide foundry using an open foundry model was established. Four Institute members committed to develop power electronic devices in this facility. This leverages existing silicon foundry capacity that was underutilized and creates a new business model for US industry to fabricate wide bandgap power electronic devices at lower cost.

Institute member projects also demonstrated and qualified advanced power modules and devices that will impact transportation, aerospace, renewable energy sectors and the power grid, that are of higher performance than silicon. These devices are being evaluated by end-users who desire to build smaller, lighter and more efficient systems than the current generation systems that rely on silicon devices.

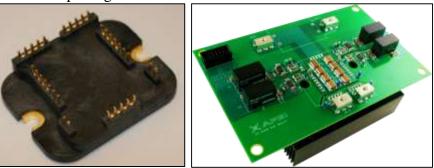

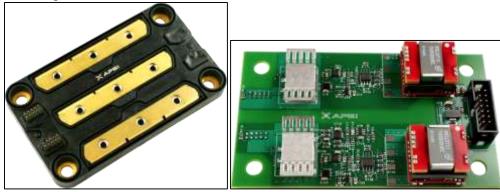

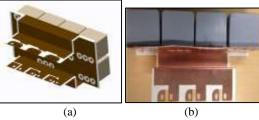

**Focus Area 3: Power Module Development and Manufacturing:** A member company released two new power module products that have lower inductance and capacitance and better thermal properties that allow wide band gap semiconductors power devices to operate closer to their theoretical limits. This company was also acquired by another Institute member.

Focus Area 4: Accelerating Power Electronic Application Commercialization Power electronic application demonstrations include design and assembly of:

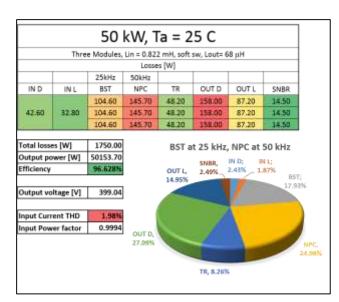

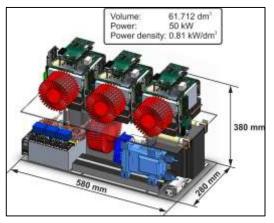

- A 50 KW fast charger for electric vehicles that is 10 times smaller than the state of the art.

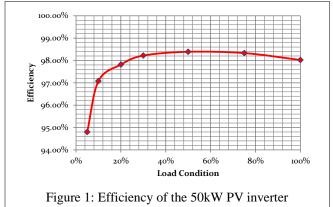

- Robust, compact inverters for photovoltaic and electric vehicle applications.

- High frequency, high power density power supplies that have the potential to significantly reduce the power consumption of data centers.

**Focus Area 5: Education and Workforce Development:** PowerAmerica successfully developed a wide bandgap power electronics concentration and curriculum within NC State University's Professional Science Master Degree program. PowerAmerica has also interacted with hundreds of students and teachers by engaging with community college

instructors, High School teachers, the NSF Advanced Technology Education program, the NIST Manufacturing Extension Partnership, and industry associations such as the Research Triangle Clean Tech Cluster to build a pipeline for a skilled workforce in the area of wide bandgap power electronics.

# **Operations and Management**

**Focus Area 1:** In its first year of existence, PowerAmerica is fully operational and has made, and is continuing to make significant strides toward meeting the 5 year goals and objectives of the Institute:

- 1. Form a self-sustaining Institute with an operating budget of \$4,000,000 per year in non-federal funds. Partner with industry, academic, and government stakeholders to promote the adoption and manufacturing of WBG semiconductors in power electronics.

- 2. Reduce the cost and scale-up the production of WBG semiconductor power devices and modules through innovative foundry models and innovations in manufacturing that result in 10,000 WBG wafers per year developed by Members within 5 years.

- 3. Have Members of the Institute perform targeted applied research and focused commercialization projects. Conduct evaluations of WBG device reliability and system level performance advantages that will de-risk industry WBG product development cycles and decrease the time to WBG-enabled products, leading to commercialization of 10 WBG PE technologies within 5 years.

- 4. Develop an educated workforce that will have the capability to innovate new WBG-enabled products to meet the future demands of WBG manufacturing, including at least 500 workers with certified skills aligned with industrial Member needs within 5 years.

In order to facilitate these goals, PowerAmerica established its headquarters on Centennial Campus at NC State University. Located at 930 Main Campus Drive, Raleigh NC is the 9,000 square foot headquarters facility that serves two distinct purposes: Administrative space occupies approximately 4,000 square feet, which houses all management offices as well as workstations, and collaboration stations, and the remaining 5,000 square feet is primarily utilized for Education and Workforce development activities. PowerAmerica members and the larger NC State community have access to break out rooms, large conference rooms, individual workstations and communal areas to gather, learn and teach. PowerAmerica is also undertaking the establishment of a Teaching Manufacturing Line within the Varsity Research Building, also on Centennial Campus, that will provide an additional 7,000 square feet of space that will not only house the associated equipment, but will also provide a space for contract fee-for-service testing and reliability efforts and research laboratory space with the capability to perform export controlled and ITAR work in a secure environment.

**Leadership and Organization**: Driving the direction of the Institute, under the leadership of MG Justice and Dr. Muth, are the development and adherence to the Operations Plan, Communications Plan, and Marketing & Branding Plan, all of which have been completed and approved by the Executive Committee. These plans define the methods by which the Institute will recruit new members, plan and conduct the yearly

Call for Projects, manage the activities of the Institute internally, and establish, manage and terminate existing and new projects. Further, these guidelines shape how the Institute engages with its constituencies, including disseminating information to the membership and committees, communicating the vision of the leadership and the Institute to employees and stakeholders, and ensuring how all of the vital roles within the organization will collectively contribute to the success and sustainability of the Institute. Of critical importance to the viability of the Institute, PowerAmerica has developed the necessary processes and procedures for maintaining the integrity of proprietary information, ensuring compliance with all applicable laws and best practices, as well as ensuring export compliance for technology developed under the cooperative agreement.

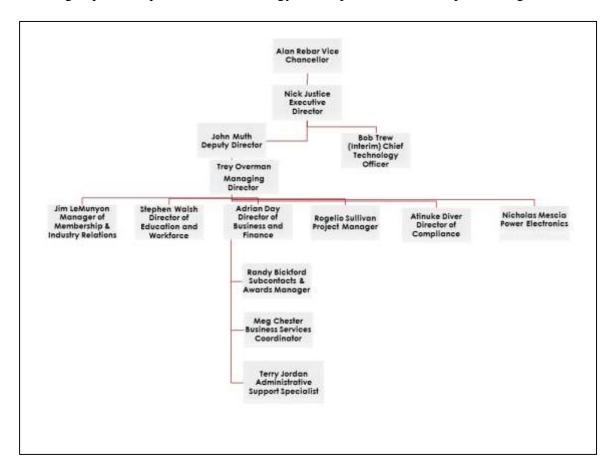

#### **PowerAmerica Organization**

PowerAmerica staffing is virtually complete. Eleven out of twelve key personnel have been appointed, including MG Nickolas Justice as the Executive Director and Dr. John Muth as the Deputy Director. A search for the remaining position of a Chief Technology Office is in process with 20 applicants being considered. The key personnel of PowerAmerica are as follows:

| Position                                         | Name             | Major Duties                                                                                                                                                                                       |

|--------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Executive Director                               | Nick Justice     | Provide visionary leadership, strategic direction, set policy and standards, sustainability planning, network with Government and industry peers                                                   |

| Deputy Director                                  | John Muth        | Implement Vision, and execute mission. Day to day operations & management, supervise staff, strategic planning, Focus on Sustainability. Liaison with DOE & other Gov., coordinate advisory boards |

| Chief Technology Officer                         | TBD              | Provide technical expertise in Institute activities, assess technology and market trends and position Institute for success; lead road mapping                                                     |

| Director of Membership and<br>Industry Relations | Jim LeMunyon     | Recruit and service industry members, create the value proposition, promote Institute broadly, support Industry Advisory Group                                                                     |

| Director of Education and<br>Workforce           | Stephen Walsh    | Lead and execute education plan, coordinate member education services, liaison with ATE/MEP, recruit students, plan & execute training program                                                     |

| Project Manager                                  | Rogelio Sullivan | Generate planning documents & operating procedures, organize reviews, grant writing, report to DOE, liaison with university organizations                                                          |

| Director of Compliance                           | Tinu Diver       | Provide information security, maintain membership agreement & bylaws, ITAR, EAR, export controls, IP management                                                                                    |

| Director of Finance and Business                 | Adrian Day       | HR management, business & financial management, financial planning & reporting                                                                                                                     |

| Subcontracts and Awards<br>Manager               | Randy Bickford   | Membership onboarding, tracking invoices and cost share, negotiating and managing subawards                                                                                                        |

| Business Services Coordinator                    | Margaret Chester | Supports business manager, manage website and information management, documents and external communications                                                                                        |

| Administrative Support Specialist                | Terry Jordan     | Equipment and facility management, supplies, support staff, visitors and events                                                                                                                    |

| Power Electronics Assembly<br>Manager            | Nicholas Mescia  | Layout proposed PCB assembly process, equipment needs, and estimate costs                                                                                                                          |

In addition to internal staff at PowerAmerica, the Institute has formed and called upon the Executive Committee and Member Advisory Committee to provide guidance and oversight. Additional expertise within the university has also been called upon to supplement the core team and contribute in key areas.

**Budget and Finance**: Under the direction of Adrian Day, the Director of Finance and Business, a preliminary resource plan has been completed and submitted. This plan addresses staffing, equipment, facility requirements, current services as well as identifying the needs of research teams within NC State University. Within this resource plan, the PowerAmerica Institute is not only solvent, but also on a well-defined path to sustainability. In addition to the resource planning already undertaken, detailed analysis has been performed to project growth models for the Institute, labor and expense planning, identifying and evaluating new potential revenue streams and infrastructure

As identified in the preliminary resource plan, the internal budget for Budget Period 1 is as follows:

| Revenue Sources         |                 |

|-------------------------|-----------------|

| Membership Fees         | \$<br>1,030,000 |

| ORIED support           | \$<br>253,000   |

| New Federal Projects    | \$<br>-         |

| New Insustry Projects   | \$<br>-         |

| DOE Funds               | \$<br>1,677,567 |

| Cost Share Support      |                 |

| State of NC             | \$<br>2,200,000 |

| F&A Returns             | \$<br>470,799   |

| NCSU Cost Share Support | \$<br>2,780,148 |

| Total Revenue           | \$<br>8,411,514 |

| Operational Expenses    |                 |

| Management Staff        | \$<br>1,469,925 |

| Rent                    | \$<br>147,582   |

| Marketing               | \$<br>100,000   |

| Travel                  | \$<br>210,000   |

| Events                  | \$<br>50,000    |

| Summer Activities       | \$<br>10,000    |

| Materials/Supplies      | \$<br>550,000   |

| Equipment               | \$<br>628,765   |

| Varsity Space Expenses  | \$<br>538,000   |

| Project Expenses        |                 |

| Faculty                 | \$<br>795,867   |

| Postdocs                | \$              |

| Students                | \$<br>294,788   |

| Equipment               | \$<br>461,168   |

| Materials/Supplies      | \$<br>330,000   |

| F&A                     | \$<br>2,053,738 |

| Total Expenses          | \$<br>7,937,332 |

| Net                     | \$<br>474,182   |

The overall Institute budget for Budget Period 1, including sub-award projects is as follows:

| CATEGORY                     | Budget Period 1<br>Costs |

|------------------------------|--------------------------|

| Institute Personnel & Travel | \$3,107,148              |

| Institute Equipment          | \$1,141,133              |

| Institute Supplies           | \$418,427                |

| f. Contractual               |                          |

| Sub-recipient                | \$26,012,130             |

| Vendor                       | \$148,878                |

| FFRDC                        | \$350,000                |

| Total Contractual            | \$26,511,008             |

| g. Construction              | \$0                      |

| h. Other Direct Costs        | \$949,826                |

| Total Direct Costs           | \$32,127,543             |

| i. Indirect Charges          | \$2,505,595              |

| Total Project Costs          | \$34,633,138             |

In addition to planning for resources in Budget Period 1 and beyond, the PowerAmerica Institute has made significant accomplishments in establishing the internal mechanisms and protocols for income-generating activities including member fees, contract research, and fee-for-service activities. A variety of collaboration instruments and accounts have also been established to facilitate these activities. Specifically, accounting structures for employees, faculty and sub awardees are functional as are internal accounts to accept membership fees with corresponding subaccounts to establish funds for member-sponsored projects, sustainability planning, marketing and other membership-funded activities. Additionally, standard operating procedures have been established and are guiding instances of in-kind contributions, fee-for-service activities and other revenue generating events.

Membership: Under the leadership of Jim LeMunyon, Manager of Membership & Industry Relations, the Institute is executing the membership recruitment strategies to develop targets for early adopter candidates, sustaining, full, and affiliate membership and engagements with these candidates are underway and will continue. Strategies for engaging with the larger technical community and other potential members, through conferences, trade shows, symposiums and other events are underway and ongoing. Building upon the membership recruiting efforts, Mr. LeMunyon is undertaking the Strategic Planning process for the Institute to drive the long-term success and sustainability of the Institute. A strategic planning kickoff meeting attended by PowerAmerica staff and the Membership Advisory Board was held on December 3<sup>rd</sup> 2015 to gather inputs and define the strategic vision for the Institute. A series of future meetings will be scheduled to perform SWOT analysis, define the strategies to capitalize on opportunities and identify strategic issues and address potential resource gaps. The plan is being developed and will all culminate in the first report on strategic planning analysis in March 2016.

Membership by level

Road mapping: Dr. Robert Trew, Interim Chief Technology Officer, in cooperation with Dr. Muth, has initiated the Technology Roadmap for the Institute, which will be a key driver for informing the Institute's strategic planning process and identifying market and technology trends that will help shape the success of the Institute. A series of meetings conducted between members of PowerAmerica staff, Dr. Trew and DOE on consensus for the expected product have been conducted and Dr. Trew is currently laying out a detailed plan for producing this roadmap. During the early planning process, two Yole reports were identified for acquisition and are being pursued to guide the development of the PowerAmerica roadmap. At present, Dr. Trew is conducting discussions with various experts and getting different opinions regarding market and technology tradeoffs. Working groups amongst the membership and other subject-matter-experts will be formed in the near future, and these groups will help to develop the detailed Technology Roadmap.

**Call for Projects**: In October 2015, PowerAmerica initiated its first Call for Projects to award new technical and education & workforce projects for Budget Period 2. This call has received an enthusiastic response from existing and potential new members. In total, 93 concept papers were received within the following focus areas:

- 20 in Foundry Operations (Focus Area 2)

- 17 in Packaging, Power Electronics Foundry, Test & Reliability (Focus Area 3)

- 46 in Accelerating WBG Adoption for Power Electronics Applications (Focus Area 4)

• 10 in Education and Workforce Development (Focus Area 5)

During the initial compliance screening on 26 October, only one concept paper was deemed to be non-compliant and the remaining concept papers were sent to external reviewers, with individual WebEx sessions held, by Focus Area, with the reviewers to generate a formal recommendation, by Focus Area, for encouraging or discouraging the submission of Full Applications. Out of the 92 concept papers that were sent for external review, 57 papers were encouraged for Full Applications, with the respective totals by focus area as follows:

- 12 in Foundry Operations

- 8 in Packaging, Power Electronics Foundry, Test & Reliability

- 29 in Accelerating WBG Adoption for Power Electronics Applications

- 8 in Education and Workforce Development

### Milestone summary as of Dec 1, 2015

| Milestone<br>No. | Short Title                                             | Due date | Status<br>(complete/incomplete,<br>notes) |

|------------------|---------------------------------------------------------|----------|-------------------------------------------|

| 1.1.1            | Executive Director Hired                                | Month 3  | Complete                                  |

| 1.1.2            | Institute Staffing Plan<br>Submitted to DOE             | Month 3  | Complete                                  |

| 1.1.3            | By-laws agreed to by sub-<br>recipients                 | Month 3  | Complete                                  |

| 1.1.4            | Staffing plan hires identified and committed to         | Month 6  | Complete                                  |

| 1.1.5            | Remaining Institute leadership positions hired          | Month 12 | On-track                                  |

| 1.1.6            | Preliminary Resource Plan submitted                     | Month 3  | Complete                                  |

| 1.1.7            | Initial headquarters operational                        | Month 6  | Complete                                  |

| 1.1.8            | Long-term resource plan reviewed by Executive Committee | Month 12 | On-track                                  |

| 1.1.9            | Lab and office space is operational                     | Month 14 | On-track                                  |

| 1.1.10           | Operations and<br>Communications Plan first<br>draft    | Month 3  | Submitted                                 |

| 1.1.11           | Internal website operational                            | Month 6  | Complete                                  |

| 1.1.12           | Internal communication executed according to plan       | Month 9  | Submitted                                 |

| Milestone | Short Title                                                         | Due date | Status                                                          |

|-----------|---------------------------------------------------------------------|----------|-----------------------------------------------------------------|

| No.       |                                                                     |          | (complete/incomplete,<br>notes)                                 |

| 1.2.1     | Membership agreement submitted to DOE                               | Month 3  | Complete                                                        |

| 1.2.2     | Secure data exchange preliminary method established                 | Month 3  | Complete                                                        |

| 1.2.3     | Risk mitigation strategies implemented                              | Month 3  | Complete                                                        |

| 1.2.4     | Membership recruitment strategy submitted to DOE                    | Month 6  | Complete                                                        |

| 1.2.5     | Membership candidates identified by category                        | Month 12 | On-track                                                        |

| 1.2.6     | Voice of the customer report on the Institute                       | Month 12 | On-track                                                        |

| 1.2.7     | Financial targets for sustainability report                         | Month 14 | On-track                                                        |

| 1.2.8     | Catalog of existing services                                        | Month 5  | Submitted                                                       |

| 1.2.9     | Report on strategy to attract contract research                     | Month 12 | On-track                                                        |

| 1.2.10    | Report on feasibility of new services for members                   | Month 14 | On-track                                                        |

| 1.2.11    | Report on feasibility for business opportunity for software package | Month 12 | Deletion of this milestone<br>requested in the Recovery<br>Plan |

| 1.2.12    | Formal agreement with member investments formalized                 | Month 14 | Deletion of this milestone requested in the Recovery Plan       |

| 1.2.13    | Marketing and Branding and External Communications Plan             | Month 5  | Submitted                                                       |

| 1.2.14    | Knowledge Distribution<br>Strategy Report                           | Month 12 | On-track                                                        |

| 1.2.15    | Institute Positioning Plan<br>Report                                | Month 12 | On-track                                                        |

| 1.3.1     | Data repository for strategic planning information                  | Month 5  | Submitted                                                       |

| 1.3.2     | Training for all members on strategic planning performed            | Month 12 | On-track                                                        |

| 1.3.3     | First report on strategic planning analysis                         | Month 14 | On-track                                                        |

| Milestone | Short Title                                        | Due date       | Status                         |

|-----------|----------------------------------------------------|----------------|--------------------------------|

| No.       |                                                    |                | (complete/incomplete,          |

|           |                                                    |                | notes)                         |

| 1.3.4     | Report on second cycle of                          | Month 14       | Deletion of this milestone     |

|           | strategic planning analysis                        |                | requested in the Recovery      |

| 1.2.5     | 26 1 11:                                           | 3.5 .1.5       | Plan                           |

| 1.3.5     | Member Advisory                                    | Month 5        | Deletion of this milestone     |

|           | Committee majority recommended list of             |                | requested in the Recovery Plan |

|           | roadmap items                                      |                | 1 Ian                          |

| 1.3.6     | Member Advisory                                    | Month 14       | On-track                       |

| 1.3.0     | Committee majority                                 | TVIOITII I I   | on track                       |

|           | recommended Industry                               |                |                                |

|           | Technology Product Draft                           |                |                                |

|           | Roadmap                                            |                |                                |

| 1.3.7     | Report on survey response                          | Month 14       | On-track                       |

|           | from at least two thirds of                        |                |                                |

|           | Institute members                                  |                |                                |

| 1.3.8     | Member Advisory                                    | Month 14       | On-track                       |

|           | Committee majority                                 |                |                                |

|           | approved Industry                                  |                |                                |

|           | Technology Product Final<br>Roadmap                |                |                                |

| 1.3.9     | Private Roadmap refined and                        | Month 14       | On-track                       |

| 1.0.9     | Public Roadmap released                            | 1,101111111111 | on their                       |

| 1.3.10    | Accounting structure in place                      | Month 3        | Complete                       |

|           | and demonstrated                                   |                | -                              |

| 1.3.11    | Draft accounting instrument                        | Month 5        | Complete                       |

|           | set up and demonstrated                            |                |                                |

| 1.3.12    | Accounts set up and                                | Month 3        | Complete                       |

|           | demonstrated                                       |                |                                |

| 1.3.13    | In-kind and industry-                              | Month 3        | Complete                       |

|           | sponsored standard operating                       |                |                                |

| 1 2 1 4   | procedures in place                                | M 4 2          | C 1.4                          |

| 1.3.14    | Fee-for-service activity                           | Month 3        | Complete                       |

|           | standard operating                                 |                |                                |

| 1.3.15    | procedures in place  Proft of detailed analysis of | Month 8        | Complete                       |

| 1.3.13    | Draft of detailed analysis of operating costs      | MIOHH 9        | Complete                       |

| 1.3.16    | Draft of detailed analysis of                      | Month 5        | Complete                       |

| 1.5.10    | potential revenue sources                          | IVIOIIIII J    | Complete                       |

| 1.3.17    | Draft of detailed                                  | Month 8        | Deletion of this milestone     |

|           | infrastructure investment                          |                | requested in the Recovery      |

|           | plan                                               |                | Plan                           |

|           |                                                    |                | =                              |

| Milestone<br>No. | Short Title                                                     | Due date | Status<br>(complete/incomplete,<br>notes) |

|------------------|-----------------------------------------------------------------|----------|-------------------------------------------|

| 1.4.1            | Operational Plan                                                | Month 5  | Submitted                                 |

| 1.4.2            | RFP for open competition fund issued                            | Month 8  | Submitted                                 |

| 1.4.3            | Selection of at least three projects from open competition fund | Month 11 | Submitted                                 |

| 1.4.4            | Subcontracts for open competition fund projects completed       | Month 14 | On-track                                  |

| 1.4.5            | RFP for membership-funded projects issued                       | Month 14 | On-track                                  |

### **Education and Workforce Development**

**Focus Area 5:** Formally, the Education and Workforce Development Team (EWDT) has been in existence since October 1, 2015 when Steve Walsh officially became the Director of Education and Workforce Development; however, portions of the team began to be assembled in the late-June to early July 2015 timeframe. Specifically, under the leadership of Dr. Gail Jones, and with the assistance of Dr. Elysa Corin and STEM Education PhD candidate Emily Cayton, they were able to organize and initiate the PowerAmerica Summer Institute. (Note that Dr. Corin has left the team, having accepted a postdoctoral position at Harvard University.)

**K12:** In addition to having the established relationship with the Friday Institute through Dr. Jones, the EWDT is expanding that relationship to possibly include work that is being done by Dr. Glenn Kleiman's team on MOOCEd technology—relationships have been established and discussions are ongoing. Planning the objectives, curricula, marketing, promotion, logistics, cost estimates, and timeline for the high school teachers' portion of the 2016 Summer Institute is underway.

It should be noted that it is not the intention of the PowerAmerica Institute to create a standalone national K12 STEM education initiative. The intention of the Institute is to work with and through the STEM researchers at the NC State College of Education and the Friday Institute to help ensure that age appropriate pedagogy regarding energy—generation, conservation, and efficiency—provided by WBG semiconductors and the products they enable are developed and distributed—in part—through their local and national networks at the K12 level.

**Community College:** Contact has been initiated with several of the appropriate NSF Advanced Technology Education Centers. These centers focus exclusively on strengthening technician level skills and education that is critical to our nation. The EWDT continues its conversations with the leadership of these centers while strategizing on different alternatives for moving forward in collaborations that promote PowerAmerica's mission.

Planning the objectives, curricula, marketing, promotion, logistics, cost estimates, and timeline for the community college instructors' portion of the 2016 Summer Institute is underway. But, much more dialogue needs to take place among the EWDT, ATEs and the targeted community colleges in order to develop an effective and efficient program of instruction for the 2016 Summer Institute.

It should be noted that it is not the intention of the PowerAmerica Institute to create a standalone WBG power electronics program for technician-level training at the community college level. Rather, it intends to collaboratively develop with the appropriate stakeholders means and methods to incorporate needed WBG semiconductor knowledge and skills into existing programs.

**Undergraduate:** The PowerAmerica URS (Undergraduate Research Scholars) program is considered the flagship program of EWD. The students targeted for this program are those with aspirations to pursue graduate degrees (MS and/or PhD) and to become the future leaders in the WBG power electronics industry. The URS program will be modeled after a similar program developed by Dr. Jones at the ASSIST (Advanced Self-Powered Systems of Integrated Sensors and Technologies) Center. Important differences between the two programs will include required interaction with industry partners and both an academic year URS version as well as a summer URS. (Note, both URS versions will have as one of their goals the recruitment and retention of women and minorities; however, extra emphasis will be placed on this during the summer URS.) In addition, collaborations with the NC State DELTA (Distance Education and Learning Technology) organization began, to discuss the possible creation of online educational modules dedicated to the world of WBG power electronics education. Lastly, the team anticipates a special section of the College of Engineering's Engineering Entrepreneurship Program sponsored by PowerAmerica and its members and dedicated to promoting senior design projects that use WBG power electronics components or products.

While discussions with industry are still in their preliminary stages, and the Needs Assessment Survey is ongoing, the trend appears to be pointing toward industry's preference for hiring students from academic institutions whose educational programs provide undergraduates an opportunity to pursue courses in power electronic/systems theory and that incorporate an extensive hands-on portion of the courses to projects.

Dr. Muth and MG Justice address undergraduate engineering students

Graduate: The Professional Science Master (PSM) EPSE (Electric Power Systems Engineering) Program with a concentration in WBG semiconductors has been established, with an online version to hopefully follow soon. The PSM dedicated solely to WBG semiconductors has been placed on hold pending further investigation regarding the needs of industry and the resources required to support its creation and operations. Part of this investigation is that the EWDT is in the process of studying and articulating the new skill sets required to design and build WBG semiconductor products and what level of education these new specialized employees will require. Preliminary investigations point toward the masters' level with concentrations in power electronics and/or power systems both incorporating extensive hands-on training over and above simple projects. Professional skills training (project management, risk assessment, communications) will be a valuable enhancement to the core engineering curriculum. PhDs will be hired for highly specific investigations in large corporations and for both design and specific investigations in SMEs—regardless, their numbers will be a small percentage with respect to the masters' level.

**Professional:** The EWDT has created and administered the first of several surveys to its members to collect data on the skills their companies need now and into 2020. Preliminary results are being collected at this time. One of our goals is to ensure the team

tracks the training of people to the technology adoption curve of WBG semiconductors. The EWDT does not want to train individuals for jobs that may not exist when they graduate. In collaboration with Phil Mintz of NC State's Industrial Extension Service, the EWDT has established relationships with MEPs from four states. (The MEP [Manufacturing Extension Partnership] is part of NIST.) Lastly, the team continues to reach out to professional organizations such as SMTA, IEEE, ASEE, ASME, etc., to establish working relationships on education and workforce training; however, more planning needs to be completed.

#### **Additional EWD Initiatives:**

- 1. **EWD 5-Year Strategic Plan:** Work has commenced on an EWD 5-Year Strategic Plan (SP). The SP will include an overall 5-year vision for EWD, its tactical mission for Budget Period-2 (BP2), a completed business model canvas (see Alex Osterwalder at www.businessmodelgeneration.com/canvas/bmc), detailed assumptions, required validation points, projected resource requirements, and pro forma financials. Projections will be headcount driven: monthly for BP2, quarterly for BP3, and yearly thereafter.

- 2. EWDAB (Education and Workforce Development Advisory Board): The EWDAB is in the process of being formed. Meetings have been held and professional evaluators have been identified. The EWDAB will be composed of five-persons representing highly connected professionals from STEM education research at the NC State College of Education and the Friday Institute, a dean of engineering/technology from the State of North Carolina Community College System, the current chair of the NC State College of Engineering Course and Curriculum Committee, a workforce development executive from an industry member corporation, and the PowerAmerica director of education and workforce development. The charter for the EWDAB is still under development. Liaisons from all PowerAmerica Institute members will provide input and feedback to the work performed and proposed by the EWDAB.

- 3. **PowerHouse:** EWDT has begun work on the concept of the PowerAmerica PowerHouse. The PowerHouse will be a multidisciplinary product design, manufacturing, & rapid prototyping facility dedicated to training the next generation of technology innovators, inventors, and educators in the art-and-science of manufacturing and technology commercialization of products enabled by WBG power electronics. At the core of the PowerHouse Concept is the teaching-manufacturing laboratory that will provide the low to medium manufacturing volume outlet for PowerHouse innovation. The PowerHouse is expected to be a transformational game-changer in advanced manufacturing education in the area of energy conservation and efficiency enabled by WBG-based power electronics.

In the end, DoE recommended that the PowerHouse concept be abandoned. They expressed reservations about its viability, costs, and fit with the mission of the Institute.

4. **PowerUP:** The EWDT is exploring the concept of a PowerAmerica accelerator program. PowerUP would be open to all students, faculty and Institute members. The central concept of PowerUP is to rapidly prove value in the marketplace of WBG-enabled products and move them quickly toward commercialization through external investment instruments. In addition, a central tenet of PowerUP is that it be professionally operated by a former/current entrepreneur/investor with significant operational experience in technology commercialization.

The PowerUP concept was not implemented due to several factors including the funding needs and the external support required to sustain it.

## Milestone Summary as of Dec 1, 2015

| Milestone<br>No. | Short Title                                                                                                                                                 | Due date | Status (complete/incomplete, notes) |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|

| 5.1.1            | Develop a needs assessment survey                                                                                                                           | Month 3  | Submitted                           |

| 5.1.2            | Administer the needs assessment survey                                                                                                                      | Month 6  | Submitted                           |

| 5.1.3            | Contact relevant NSF<br>ATE Centers and<br>identified existing skills<br>standards                                                                          | Month 9  | Submitted                           |

| 5.1.4            | Identify six critical skill areas at the technician and engineer levels needed for training                                                                 | Month 14 | On-track                            |

| 5.1.5            | NC MEP Center<br>identified MEP centers in<br>three states to assist with<br>dissemination of program<br>information, materials,<br>marketing, and outreach | Month 3  | Submitted                           |

| 5.1.6            | Materials have been developed and strategic outreach plans are in place for four MEP Centers                                                                | Month 6  | Submitted                           |

| 5.1.7            | Three hundred brochures have been distributed                                                                                                               | Month 12 | On-track                            |

| 5.1.8            | MEP Centers identified four additional potential partners                                                                                                   | Month 14 | On-track                            |

| Milestone<br>No. | Short Title                                                                                                                              | Due date | Status (complete/incomplete, notes)                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------|

| 5.1.9            | Established contacts and relationships with more than three appropriate technology related NSF ATE Centers                               | Month 3  | Submitted                                                 |

| 5.1.10           | Developed marketing materials to be distributed                                                                                          | Month 6  | Submitted                                                 |

| 5.1.11           | Distributed 100 brochures to NSF ATE Centers                                                                                             | Month 12 | On-track                                                  |

| 5.1.12           | Curriculum and resources have been developed into the courses for the training programs                                                  | Month 14 | On-track                                                  |

| 5.2.1            | The MS in Electric Power Systems Engineering Wide Bandgap Power Electronics Concentration established and two students commence program. | Month 3  | Will be submitted by 12/15/15                             |

| 5.2.2            | The two students work in labs on related Institute projects in WBG Power Electronics.                                                    | Month 6  | Will be submitted by 12/15/15                             |

| 5.2.3            | Two students complete the WBG PE design project.                                                                                         | Month 12 | On-track                                                  |

| 5.2.4            | Two students complete<br>the WBG concentration<br>program with a MS in<br>Electric Power Systems<br>Engineering.                         | Month 14 | On-track                                                  |

| 5.2.5            | Development of new courses for the PSM program                                                                                           | Month 3  | Deletion of this milestone requested in the Recovery Plan |

| 5.2.6            | Recruiting efforts for the PSM program in place                                                                                          | Month 6  | Deletion of this milestone requested in the Recovery Plan |

| Milestone<br>No. | Short Title                                                                                                        | Due date | Status (complete/incomplete, notes)                       |

|------------------|--------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------|

| 5.2.7            | The new and revised courses and labs are finalized for the PSM program                                             | Month 9  | Deletion of this milestone requested in the Recovery Plan |

| 5.2.8            | Applicants are reviewed<br>for the PSM program and<br>ten students are admitted<br>to the program for Fall<br>2015 | Month 14 | Deletion of this milestone requested in the Recovery Plan |

| 5.3.1            | Identified research projects and faculty advisors for the URS program.                                             | Month 12 | On-track                                                  |

| 5.3.2            | Developed marketing materials for the URS program                                                                  | Month 12 | On-track                                                  |

| 5.3.3            | Distributed 300 brochures and other marketing materials to university partners                                     | Month 12 | On-track                                                  |

| 5.3.4            | Reviewed applicants and selected ten URS candidates to participate in the program                                  | Month 14 | On-track                                                  |

| 5.4.1            | Curriculum and other resources from NSF ATEs and others are identified leverage for the Institute training program | Month 3  | Submitted                                                 |

| 5.4.2            | Marketing materials are developed for the community college and high school train the trainer program.             | Month 6  | Submitted                                                 |

| 5.4.3            | One hundred brochures<br>are distributed through<br>NSF ATE Centers,<br>community colleges, and<br>industry        | Month 14 | On-track                                                  |

| Milestone | Short Title                                                                                                     | Due date | Status (complete/incomplete, |

|-----------|-----------------------------------------------------------------------------------------------------------------|----------|------------------------------|

| No.       |                                                                                                                 |          | notes)                       |

| 5.4.4     | Applicants are reviewed and candidates are selected                                                             | Month 14 | On-track                     |

| 5.5.1     | External evaluator team<br>reviews all programs<br>(Summer Institute, URS,<br>PSM, short course)                | Month 12 | On-track                     |

| 5.5.2     | Evaluation team develops<br>a set of metrics and<br>surveys for the program                                     | Month 12 | On-track                     |

| 5.5.3     | Twenty-five surveys are administered to the program participants                                                | Month 14 | On-track                     |

| 5.5.4     | Data is interpreted and first report with recommendations is delivered to the Institute 's Leadership team      | Month 14 | On-track                     |

| 5.6.1     | Developed storyboards<br>for the videos and<br>develop the WBG Online<br>Portal site                            | Month 3  | Submitted                    |

| 5.6.2     | Created one online<br>module for high school<br>teachers and one module<br>for community college<br>instructors | Month 14 | On-track                     |

| 5.6.3     | Scheduled video shoot<br>and WBG Online portal<br>is developed                                                  | Month 14 | On-track                     |

| 5.6.4     | Video and educational<br>materials are available on<br>the WBG Online portal                                    | Month 14 | On-track                     |

**Institute Member Accomplishments**

Organization:

ABB Inc., Corporate Research

Task No./Project Title:

Task 2.12 / 3.3 kV SiC MOSFET Device Development

Technical Point of Contact:

VR. Ramanan, VR.Ramanan@us.abb.com

Sub-award start date:

02/01/2015

**Project Objectives:** The purpose of this task is to accelerate the development and manufacture of 3.3 kV SiC MOSFET devices using a 150 mm silicon foundry. According to various estimates, the cost of processing SiC can be up to 50% of the final device cost. Therefore, it is important to understand the major cost components and their cost reduction aspects; this can be achieved effectively by using an existing foundry. Engineering samples of these devices will be provided for wafer level testing and in discrete packages to the Institute. Faculty members at the Institute will aid in the design and process development for these devices. Evaluating the long-term reliability of the gate oxide, as well as surge current capability and other application related performance criteria would not be part of this task.

The measurable outcomes of this task will be:

- Process developed for 3.3 kV SiC MOSFETs with pathways determined for cost reduction and yield improvements to enable the cost reduction of 3.3 kV SiC MOSFETs in future budget periods.

- 2. Engineering samples of 3.3 kV SiC MOSFETs delivered to Institute for testing and analysis.

- 3. Tested 3.3 kV SiC MOSFETs in discrete devices with measured parameters and specifications.

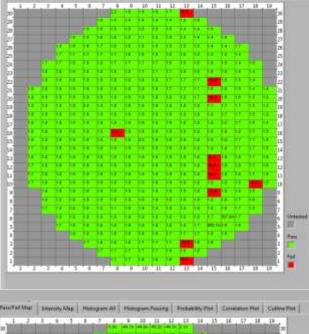

**Project's Contribution to the PowerAmerica Mission:** The main contribution of this task can be summarized in terms of reducing the cost of WBG devices. By working closely with a world-class US-based facility (XFAB), the ABB project team aims to understand the cost reduction potential of SiC manufacturing. In BP1, the focus is on evaluating the readiness of the foundry in terms of processing 6" SiC wafers with a yield >75%. A mixture of know-how in processing from ABB as well as XFAB is necessary to effectively tackle the issues of SiC processing. Additional improvements in device designs are considered for a possible BP2 extension of the Task, as discussed in more detail in chapter 7.

Through the support from PA, ABB can efficiently collaborate with XFAB, and due to our global corporate presence, generate new opportunities for the US foundry. By running our experimental lots with XFAB, we also contribute to workforce development in US, since the engineers and operators in XFAB have the opportunity to try out new processes on our lots and qualify new tools. This creates much needed US-based expertise and a new generation of foundry specialists able to handle the challenges of processing SiC wafers.

**Technical Approach:** Work to be accomplished in this task includes:

- 1. Design of 3.3 kV SiC MOSFET.

- 2. Assessment of SiC foundry process steps that are non-proprietary.

- 3. Assessment of SiC foundry process steps that will need to be transferred to the foundry.

- 4. Transfer of SiC Process to foundry.

- 5. Design of experiment and iterated three cycles of fabrication, characterization, and testing, to improve process steps to improve manufacturability.

- 6. Perform wafer level testing.

Issues, Risks and Mitigations: The sub-award has been significantly delayed by lengthy legal discussions, on which the project team had no influence of. Nonetheless, together with PA management, the project team has made significant steps to refocus the task and make sure that the deliverables can still be met (in full or partially) by the official end of BP1. For example, we proposed a concrete action of substituting one MOSFET lot with a JBS diode lot, which will shorten the processing time by about 1 month while still delivering important information about the performance of XFAB in terms of process control, yield, etc.

Most of the technical risks were tackled in the project by making sure the processes and designs needed to perform the work have been de-risked previously. Nonetheless, there is always an inherent risk related to the performance of XFAB (or their 3<sup>rd</sup> party collaborators) in handling our wafers, e.g. wafer breakage can happen, or processes can be performed under the wrong schedule. Therefore, our lots include multiple wafers and the purchase order to XFAB specifies a minimum of 3 good wafers to be delivered to ABB.

Another outstanding technical risk is the specific gate oxidation process required for MOSFETs—as XFAB does not have yet a qualified process in place, ABB has agreed to share with XFAB the use of the MOSFET lots in this project to fine tune this process. Outstanding issues: XFAB still outsources critical process steps to 3<sup>rd</sup> parties, and this introduces delays and higher costs. Once the dedicated SiC equipment in XFAB will be qualified for production in 2016, we expect a significantly lower processing time.

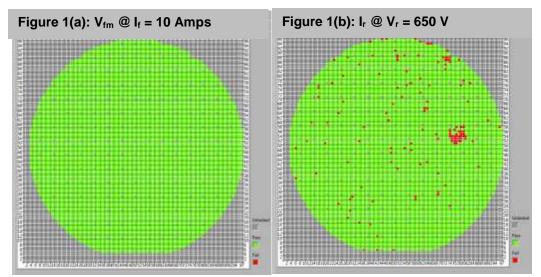

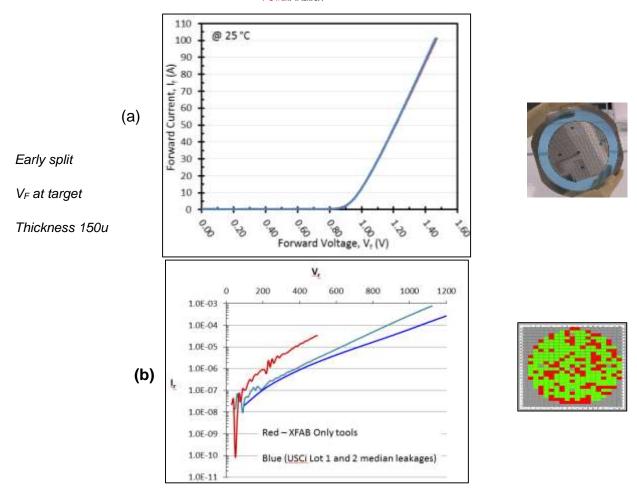

## **Significant Accomplishments:** Two significant accomplishments are outlined below:

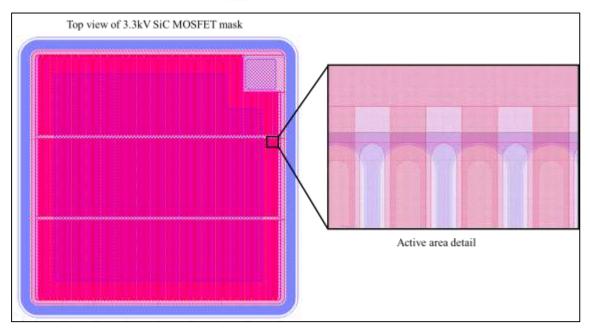

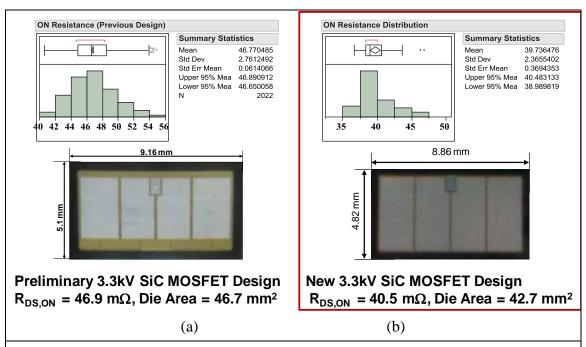

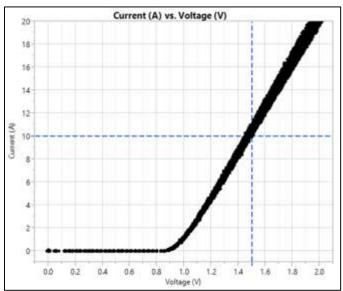

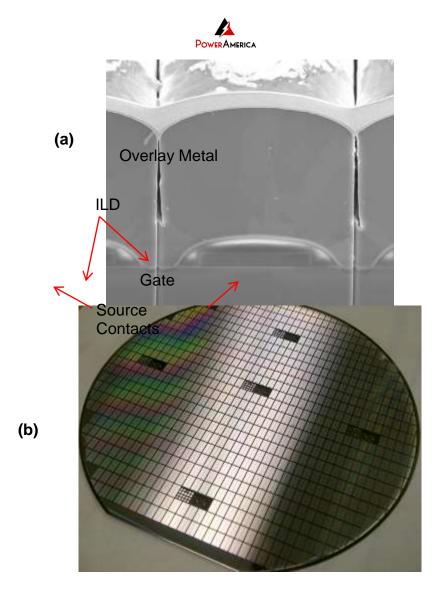

- 1. Complete design of JBS diode and MOSFET cells, including active and termination regions. In the figure below, the top layout of a MOSFET die is showed. The active area is estimated to allow for close to ideal yields. For the 3.3kV voltage class, the device area translates into a nominal current rating per device of about 25A. This design will not be modified in the next steps, while the variation in device performance due to processing artifacts will be evaluated next year once the lots are completed.

- 2. Complete process routers for JBS and MOSFETs that match the XFAB internal development status. These routers include now more than 150 detailed processing steps which have been discussed with the foundry during a 2 day site visit in Lubbock TX. The process includes now 10 masks for MOSFET, with a lead manufacturing time of approximately 3 months as communicated by XFAB.

**Technology to Market:** As mentioned in Chapter 2, the major focus of the task is still understanding the cost reduction potential through the use of the proposed PA foundry model. In BP1 we discussed extensively with XFAB their long-term pricing models were discussed extensively. With the late start of the Sub-Award, it may be more challenging to reach a clear-cut conclusion within the hard end date set for BP1. In addition, XFAB is still in the ramping phase of their line, and outsources critical process steps. This introduces additional costs and longer processing times. This situation is expected to alleviate itself after Q3'2016 when new equipment will be qualified in the foundry. In order for ABB to successfully complete the assessment of the PA proposed foundry model, we strongly argue for an extension of the activity in Year 2. This will enable our project team to process a statistically significant number of lots (at least 10, each of 6 wafers) and run enough experiments demonstrating the suitability of XFAB as THE SiC foundry of choice. Both ABB and XFAB would have gained by the end of Year 2 a clear & concise picture about the potential for future collaboration in terms of required yields, processing cost per wafer, with expected commercial volumes potentially ramping up in 2018 –pending that all required milestones are passed successfully, and that the business case offers the required ROI.

**Plans for Next Budget Period If Funded:** Due to the late start date of this sub-award ABB strongly argues that a next budget period is needed to fully exploit the potential of a partnership with XFAB. In addition, XFAB still works on upgrading the production line and fine-tuning their price models accordingly.

If the next budget period is funded, ABB will continue the work on exploring further mechanisms for cost reduction in terms of \$/A. The main focus will be identifying novel MOSFET designs and manufacturing processes that lead to reduced cost. For example, developing a design with improved current density can lead to a direct cost reduction potential since the dies can be made smaller. In the Year 1 budget, we are

focusing more on the manufacturing aspects, but an extension into Year 2 will enable more exploratory device designs to be tried out.

A possible schematic SOPO for the next budget period is given below:

| Milestone<br>No. | Short Title                                                                                                 | Due date | Notes                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.12.2.1         | Process established to<br>produce functional 3.3<br>kV SiC MOSFETs;<br>BV>3.3 kV                            | Month 4  | Based on BP1 and further lot iteration, based on "Standard" design                                                                                                                                                |

| 2.12.2.2         | New design 3.3kV SiC MOSFET with improved current density                                                   | Month 8  | Increased current density translates into smaller dies, thus lower cost per Amp. At least 20% improvement targeted.                                                                                               |

| 2.12.2.3         | Samples of 3.3 kV SiC MOSFETs with improved design and processed and wafer tested                           | Month 12 |                                                                                                                                                                                                                   |

| 2.12.2.4         | Around 10 lots of 6 wafers each are processed at XFAB based on "standard MOSFET design". Yield must be >85% | Month 12 | In BP1 only few lots could be manufactured at XFAB. This does not provide significant statistical learning and relevance for ABB in order to confirm the validity of the foundry model proposed by Power America. |

**Project Output:** No publications, conference presentations, awards/recognition, IP disclosures, or patent filings were done until now in this Task.

**Milestone Summary**

| Milestone<br>No. | Short Title                                              | Due date | Status (complete/incomplete, notes)                                                                                        |

|------------------|----------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 2.12.1.1         | 3.3 kV SiC MOSFET mask design and process flow finalized | Month 10 | Complete Agreements with foundry in place to run wafers.                                                                   |

| 2.12.1.2         | 1 <sup>st</sup> lot processed wafers                     | Month 13 | Incomplete 2 lots (JBS & MOSFET) will be started in parallel in order to account for the late start date of the sub-award. |

| Milestone<br>No. | Short Title                                                                               | Due date | Status (complete/incomplete, notes)                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.12.1.3         | Samples of 3.3 kV SiC MOSFETs are wafer tested                                            | Month 14 | Incomplete                                                                                                                                               |

| 2.12.1.4         | Baseline process<br>established to produce<br>functional 3.3 kV SiC<br>MOSFETs; BV>3.3 kV | Month 14 | Incomplete Due to the late Sub-award start date this may be a partial Go/No Go decision, since not enough lots can be processed in the given time frame. |

## Organization:

Arizona State University

(Note: Dr. Chowdury is moving UC Davis. UC Davis has been strongly supportive of PowerAmerica and is working closely with PowerAmerica to ensure that cost sharing obligations are met.)

Task No./Project Title:

2.11

Technical Point of Contact:

Dr. Srabanti Chowdhury

Sub-award start date:

02/01/2015

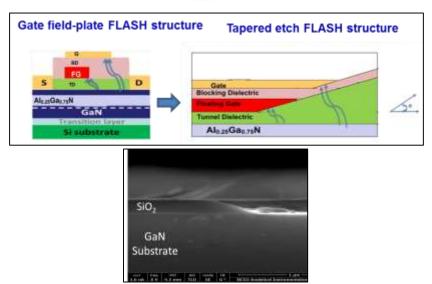

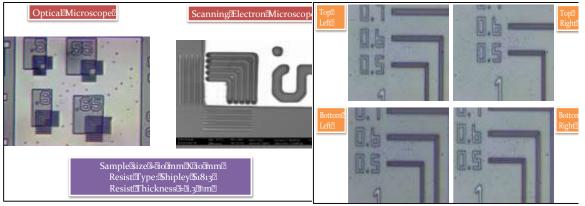

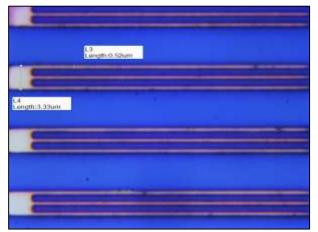

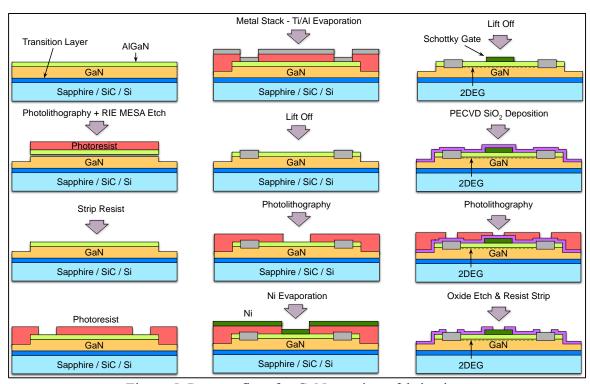

**Project Objectives:** The overarching goal of the project was to design and fabricate 600V D-Mode AlGaN/GaN HEMTs. The project was divided into 2 categories. In first category we developed and characterized the dielectric layers necessary for the device fabrication using MIS capacitors and in the second category we modeled 600V HEMTs and implemented device design based on the model to achieve 600V functional HEMTs.

**Project's Contribution to the PowerAmerica Mission:** The project developed open foundry process that will enable proliferation of GaN-based power electronic devices, which can be easily manufactured in a Si-based foundry. Our work also resulted in increased "volts-per-micron" leading to significant decrease of the chip area for a given current rating.

### **Technical Approach:**

### 3.1. Dielectric Engineering

The tasks were designed to solve reliability problems and improve performance of lateral GaN-on-Si (or GaN-on-SiC) MISHEMTs (Metal-Insulator-Semiconductor High Electron Mobility Transistors). The tasks were formulated as process modules that can be readily incorporated into a GaN foundry. Dielectrics and deposition techniques for passivation in GaN devices were studied and down-selected. Device figure of merit (FOM) enhancement through field management and dynamic R<sub>on</sub> improvements were achieved. Gate stack dielectrics for single chip D-mode devices were investigated and optimized for, reliability, breakdown and channel mobility.

The desired properties of a gate dielectric in a power device include minimal threshold voltage shift after a large positive gate bias, low interface trap density generation under stress while maintaining high channel mobility in the electron channel under the dielectric. High quality passivation dielectrics are also essential for reliable GaN-based devices at the drain side edge of the gate. Therefore, it is critical to develop good quality dielectrics for the gate oxide as well as the passivation dielectrics. Al<sub>2</sub>O<sub>3</sub> deposited by different deposition techniques such as Atomic Layer Deposition (ALD) and Plasma Enhanced ALD (PEALD) will be explored to produce reliable dielectrics that can withstand high field and high temperature. Emphasis will be placed on maintaining high quality bulk layers via the use of amorphous dielectrics. Achieving low Dyn R<sub>on</sub> is necessary for any GaN technology to achieve widespread acceptance. It is therefore included in this task as a simultaneous requirement along with the other metrics.

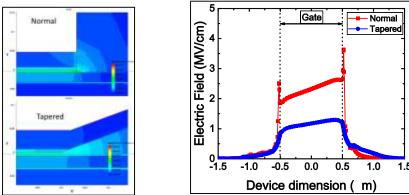

#### 3.2. Volts-per-micron enhancement

Our approach was to develop higher figure of merit devices (lower  $R_{on}$ ) by improving the lateral V/micron of breakdown field strength between the gate and the drain. The present electric field for reliable devices is <40V/ $\mu$ m (nearly an order of magnitude smaller than the theoretical breakdown field in GaN) and what has been demonstrated in vertical GaN devices. Lateral field improvement were achieved by improving electric field management. Both lateral electric field modification using implantation and field plate structures were employed to achieve the goals. Field plate design were first developed using Silvaco Atlas software (which is widely used in industry). Devices were

built and the designs were validated. This approach will readily translate into industry as the tools and methodologies will be readily transferable. Volts per micron was determined as the 80% of the breakdown voltage divided by the gate to drain spacing. The breakdown voltage was chosen judiciously to ensure stable operation of the devices and not merely a sweep voltage, which is often reported in various literatures. As a part of this task we will be setting up the criteria for reporting volts per micron.

**Issues, Risks and Mitigations:** The main issue we have faced during the development of devices in BP1 is lack of vendors to obtain high voltage compatible GaN epi on Si or SiC.

#### **Significant Accomplishments:**

In the BP1 our team was able to achieve the following milestones under the program:

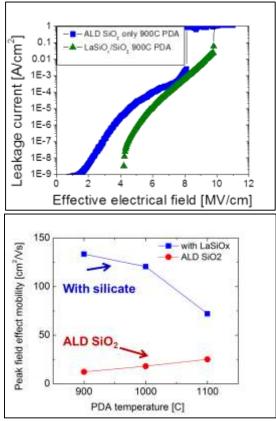

- Leakage current <10<sup>-2</sup>mA/cm<sup>2</sup> and average breakdown electric field >3MV/cm were achieved for both ALD Al<sub>2</sub>O<sub>3</sub> and PEALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics.

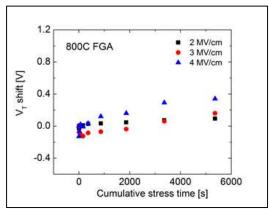

- Hysteresis <0.5V was measured; time or voltage dependent stress tests did not cause any remarkable change in C-V characteristics.

- Accurate 2D drift-diffusion model of HEMTs, which were used to optimize field plate designs.

- Field plated HEMT measuring breakdown voltages (V<sub>br</sub>) up to 900V (equivalent breakdown field 60V/μm), which is significantly higher, compared to what is offered by the state-of-the art designs.

#### **Characterization of Gate Dielectrics**

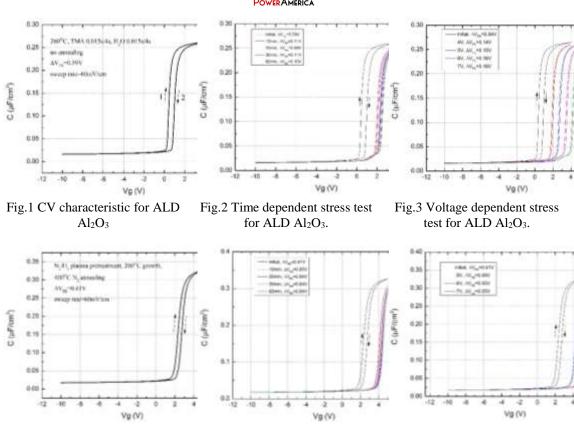

ALD Al<sub>2</sub>O<sub>3</sub> was deposited using a commercial ALD system Cambridge Savannah with the following conditions: TMA pulse 15ms/purge 4s, H<sub>2</sub>O pulse 1ms/purge 4s, 260°C deposition temperature and no post deposition annealing. The average breakdown electric field of 3.3MV/cm and a record high of 6.7MV/cm were measured. CV hysteresis was 0.59V (Fig.1). Time dependent stress test in which the MIS capacitors were held in 4V for different time durations showed a series of consistent hysteresis of ~0.1V (Fig.2). Voltage dependent stress test in which the MIS capacitors were held in different positive voltages for 10mins showed a series of consistent hysteresis of ~0.15V (Fig.3).

PEALD Al<sub>2</sub>O<sub>3</sub> was deposited using self-built PEALD system in Dr. Nemamich's group from the Arizona State University with the following conditions: pretreatment with H<sub>2</sub>/N<sub>2</sub> plasma at 680°C, 200°C deposition temperature and post deposition annealing with N<sub>2</sub> at 400°C for 15min. The average breakdown electric field of 3.6MV/cm and a record high of 8.9MV/cm were measured. CV hysteresis was 0.41V (Fig.4). Time dependent stress test showed a series of consistent hysteresis of ~0.04V (Fig.3). Voltage dependent stress test showed a series of consistent hysteresis of ~0.05V (Fig.3).

Fig.4 CV characteristic for PEALD Al<sub>2</sub>O<sub>3</sub>.

Fig.5 Time dependent stress test for PEALD Al<sub>2</sub>O<sub>3</sub>.

Fig.6 Voltage dependent stress test for PEALD Al<sub>2</sub>O<sub>3</sub>.

#### **Electrical Field Management using Field-plate (Simulation)**

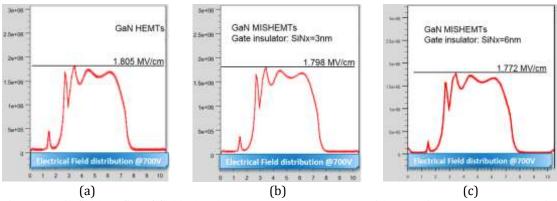

Electrical field profile of field-plated GaN HEMT (or MISHEMT) with  $L_{SD}$ =10.5 $\mu$ m and  $L_{GD}$ =8 $\mu$ m was simulated in Silvaco. The electric field peak of GaN HEMT was optimized to be 1.805MV/cm at  $V_{ds}$ =700V (Fig.7(a)). The electric field peak decreases with increasing the gate dielectric thickness (Fig.7(b) and (c)).

Fig.7 Electric field profile of field-plated (a) HEMT (b) MISHEMT with 3nm Si<sub>3</sub>N<sub>4</sub> (c) MISHEMT with 6nm Si<sub>3</sub>N<sub>4</sub>.

#### **GaN MISHEMT (Experimental)**

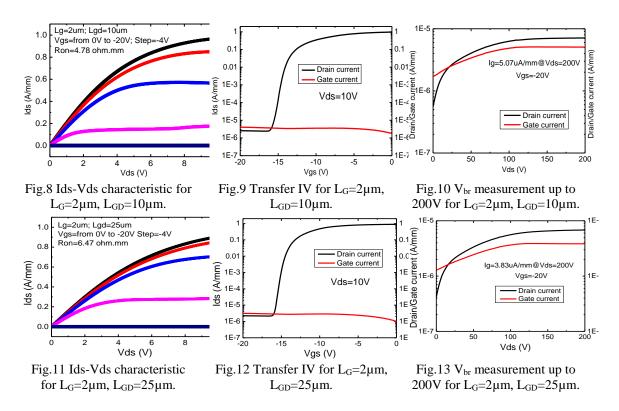

GaN MISHEMTs with  $L_{GD}$  of 5 $\mu$ m, 10 $\mu$ m, 15 $\mu$ m, 20 $\mu$ m and 25 $\mu$ m and  $L_{g}$  of 2 $\mu$ m were fabricated.  $R_{on}$  was in the range of 4-70hm·mm owing to low  $R_{c}$ =0.430hm·mm and

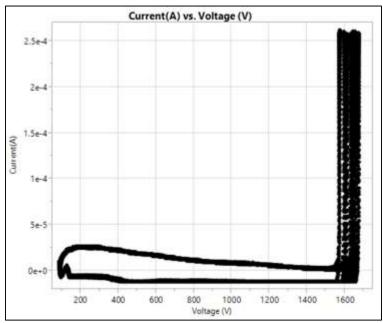

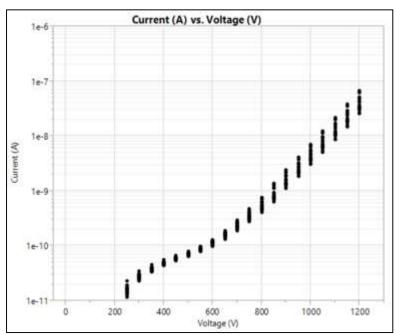

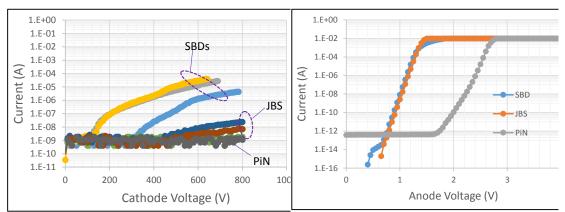

$R_{sh}\!\!=\!\!382.5\text{ohm/sq}$  extrapolated from TLM measurement. IV characteristics of the device with  $L_{GD}\!\!=\!\!10\mu m$  and  $25\mu m$  are shown in Fig.8 and Fig.11.  $V_T$  was around -16V as extrapolated from transfer IV curve (Fig.9 and Fig.12). Low  $V_{br}$  measurement was carried out in pinch-off and  $V_{ds}$  up to 200V (Fig.10 and Fig.13).  $I_g$  was  $5.07\mu A/mm$  at  $V_{ds}\!\!=\!\!-200V$  and  $V_{gs}\!\!=\!\!-20V$ . The  $I_{on}/I_{off}$  ratio was greater than  $10^5$ . Finally, an additional high  $V_{br}$  measurement was conducted on the MISHEMT with  $L_{GD}\!\!=\!\!15\mu m$ .  $V_{br}$  of over 900V was achieved using florinert during the measurement.

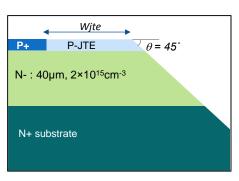

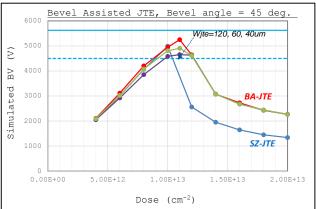

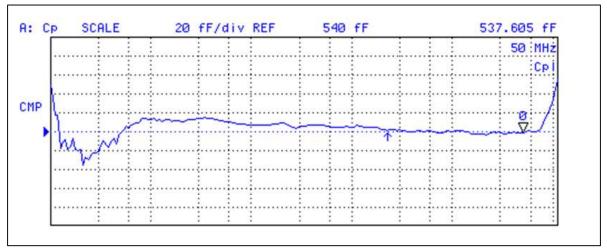

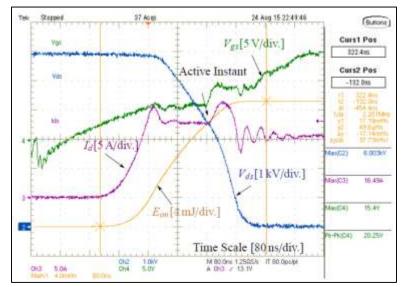

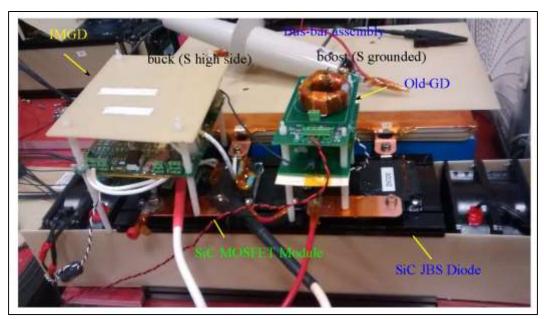

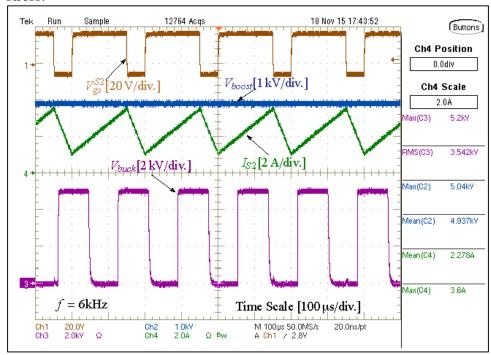

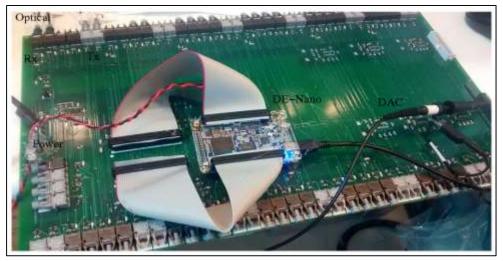

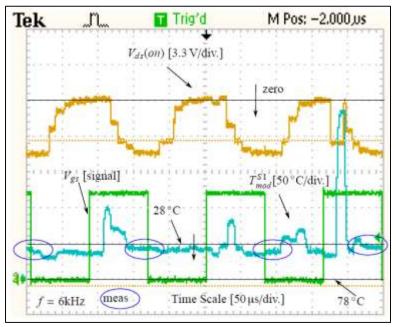

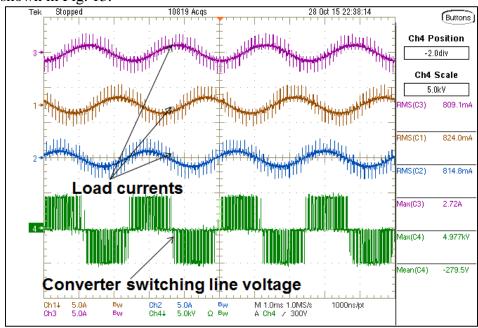

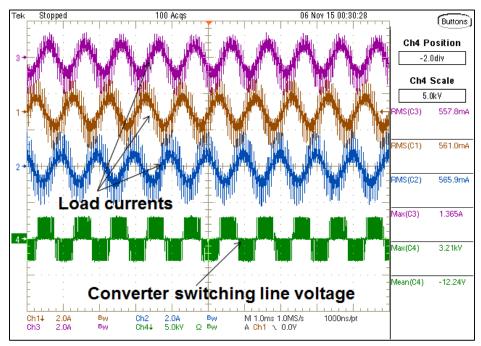

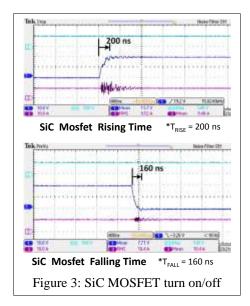

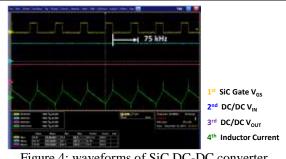

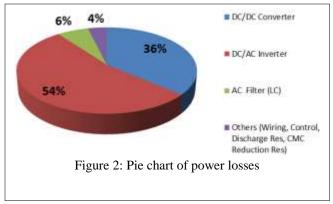

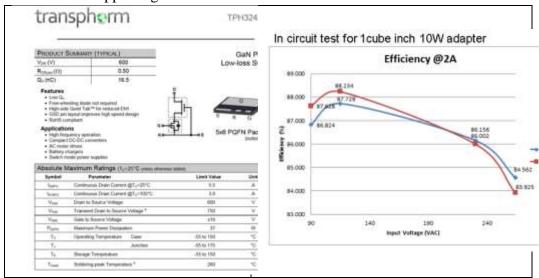

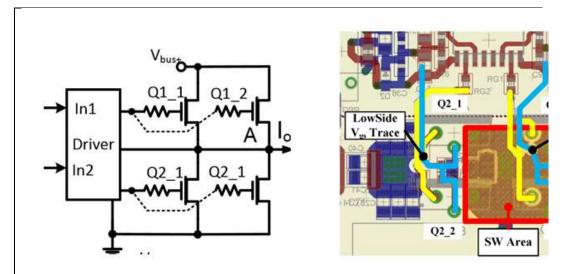

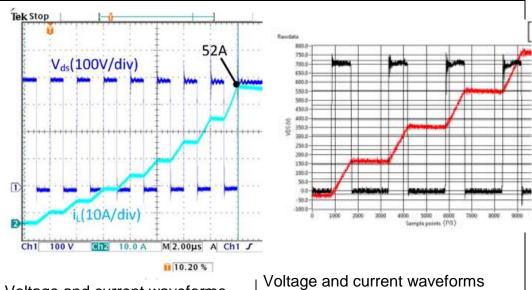

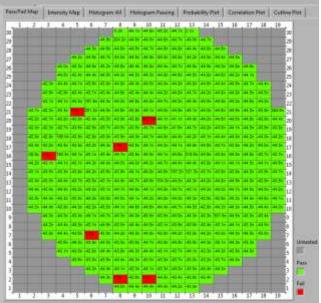

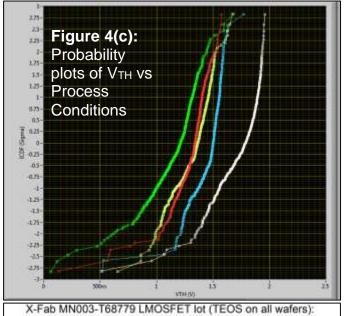

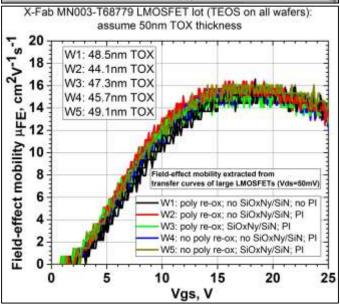

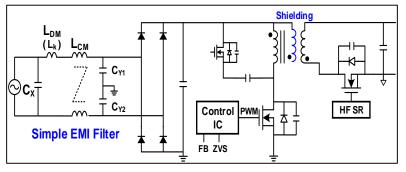

**Technology to Market:** The market for the medium power GaN extends from (few hundreds of watts to 10KW) and include 1) Motor Drives 2) Photovoltaic Inverter 3) Power supplies for data centers 4) Adapters and chargers for computers and laptops 5) Servo motors 6) power supplies for surgical tools.